# الجمهورية الجزائرية الديمقراطية الشعبية

People's Democratic Republic of Algeria Ministry of Higher Education and Scientific Research

# UNIVERSITY FERHAT ABBAS - SETIF1 FACULTY OF TECHNOLOGY

# **THESIS**

**Submitted to the Department of Electronics**

In Fulfilment of the Requirements for the degree of

# **DOCTORATE**

**Domain: Sciences and Technologies**

By

#### Abdelaziz KERBOUCHE

# **THEME**

# Optimized FPGA Implementation of Round-Based Ciphers: A High-Performance and Area-Efficient AES Implementation

**Professor**

Hamimi CHEMALI

#### Hamida Abdelhak FERHAT **Professor** Univ. Ferhat Abbas Sétif 1 **President Mouloud AYED Professor** Univ. Ferhat Abbas Sétif 1 Thesis director **Abdelhalim MAYOUF Professor Examiner** Univ. Ferhat Abbas Sétif 1 **Abdelhamid DAAMOUCHE Professor Examiner** Univ. M'hamed Bougara Boumerdes Abdellatif KHELIL **Professor** Univ. Hamma Lakhder El Oued **Examiner**

Univ. Ferhat Abbas Sétif 1

Guest

Defended on /02/2025 in front of Jury:

# الجمهورية الجزائرية الديمقراطية الشعبية

République Algérienne Démocratique et Populaire Ministère de L'Enseignement Supérieur et de la Recherche Scientifique

# UNIVERSITÉ FERHAT ABBAS - SETIF1 FACULTÉ DE TECHNOLOGIE

# **THÈSE**

# Présentée au Département d'Électronique

Pour l'obtention du diplôme de

# **DOCTORAT**

Domaine: Sciences et Technologie

Filière : Électronique Option : Électronique des Systèmes Embarqués

Par

# **KERBOUCHE Abdelaziz**

# **THÈME**

# Implémentation optimisée sur FPGA de chiffrements à base de rondes : une architecture AES performante et à faible empreinte matérielle

Soutenue le /02/2025 devant le Jury :

| FERHAT Hamida Abdelhak | Professeur | Univ. Ferhat Abbas Sétif 1      | Président          |

|------------------------|------------|---------------------------------|--------------------|

| AYED Mouloud           | Professeur | Univ. Ferhat Abbas Sétif 1      | Directeur de thèse |

| MAYOUF Abdelhalim      | Professeur | Univ. Ferhat Abbas Sétif 1      | Examinateur        |

| DAAMOUCHE Abdelhamid   | Professeur | Univ. M'hamed Bougara Boumerdes | Examinateur        |

| KHELIL Abdellatif      | Professeur | Univ. Hamma Lakhder El Oued     | Examinateur        |

| CHEMALI Hamimi         | Professeur | Univ. Ferhat Abbas Sétif 1      | Invité             |

Année: 2024-2025

# **Abstract**

Modern life relies heavily on embedded systems, which, despite their compact and resource-constrained nature, serve as the core intelligence behind most devices. These smart systems collect user data to continuously improve decision-making processes. However, the gathered data often includes sensitive information, highlighting the critical need for robust security measures that ensure trustworthiness and reliability without compromising performance. This project aims to identify an optimal implementation technique for security algorithms in embedded systems, balancing resource utilization and timing performance. The primary challenge addressed is maintaining the integrity of the security algorithm while optimizing hardware architecture to maximize efficiency. The Rijndael algorithm, specifically the Advanced Encryption Standard (AES), is chosen as the security core and implemented using two distinct techniques. The proposed approach is designed for Field-Programmable Gate Arrays (FPGAs), with results benchmarked against similar projects in terms of timing and area performance.

**Keywords**: Advanced Encryption Standard (AES) algorithm, Field Programmable Gate Array (FPGA), Cryptography, embedded systems

# **Table of Contents**

| General introduction                               | 8  |

|----------------------------------------------------|----|

| Chapter 1. Literature Review                       | 10 |

| 1.1. Limitations and challenge                     | 10 |

| 1.2. Implementation of cryptographic algorithms    | 11 |

| 1.3. Related works                                 | 13 |

| 1.3.1.New lightweight block ciphers                | 14 |

| 1.3.2.Lightweight hash functions                   | 15 |

| 1.3.3.Implementation optimization                  | 15 |

| 1.4. Conclusion                                    | 16 |

| Chapter 2. Theoretical Background on Cryptography  | 17 |

| 2.1. Introduction                                  | 17 |

| 2.2. Core Security Principles                      | 17 |

| 2.2.1.Confidentiality                              | 18 |

| 2.2.2.Integrity                                    | 18 |

| 2.2.3.Availability                                 | 18 |

| 2.2.4.Authentication                               | 19 |

| 2.3. Cryptography                                  | 19 |

| 2.4. Hashing and Hashing Algorithms                |    |

| 2.5. Symmetric cryptography                        | 21 |

| 2.5.1.Symmetric encryption                         | 21 |

| 2.5.2.Message authentication codes (MAC)           | 32 |

| 2.5.3.Pseudo Random Functions (PRF)                | 33 |

| 2.5.4.Key Derivation Function (KDF)                | 33 |

| 2.6. Asymmetric cryptography                       | 34 |

| 2.6.1.Asymmetric encryption                        | 35 |

| 2.6.2.Signatures                                   | 37 |

| 2.6.3.Key exchange                                 | 40 |

| 2.7. Block cipher operation modes                  | 41 |

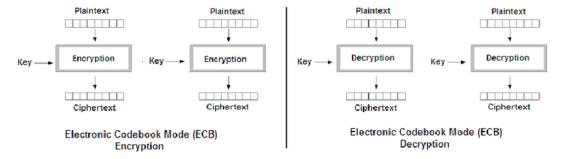

| 2.7.1.Electronic Code Book (ECB)                   | 41 |

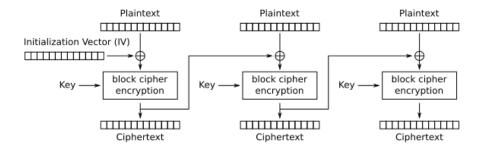

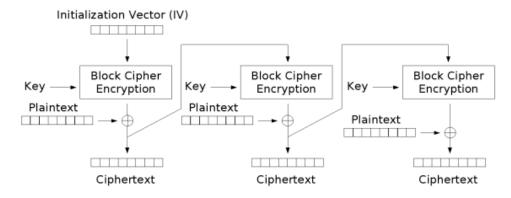

| 2.7.2.Cipher Block Chaining (CBC)                  | 41 |

| 2.7.3.Cipher FeedBack (CFB)                        | 42 |

| 2.7.4.Output feedback (OFB)                        | 43 |

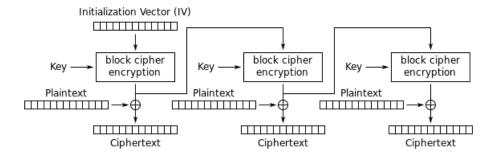

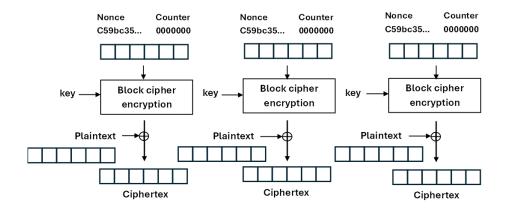

| 2.7.5.Counter mode (CTR)                           | 44 |

| Chapter 3. Hardware design optimization strategies | 46 |

| 3.1. Timing Constraints                            | 46 |

| 3.2. Clock Frequency                               | 47 |

| 3.3. Maximum frequency and timing optimization     | 49 |

| 3.4. Cells-Clock synchronization                   | 49 |

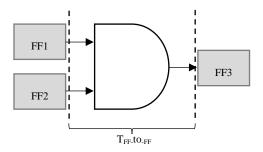

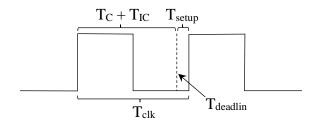

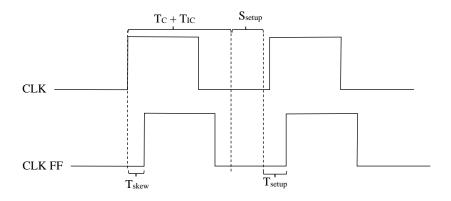

| 3.4.1.Setup times                                  | 49 |

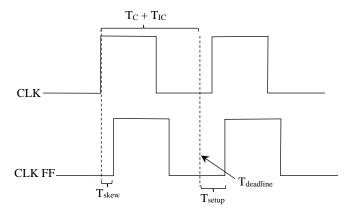

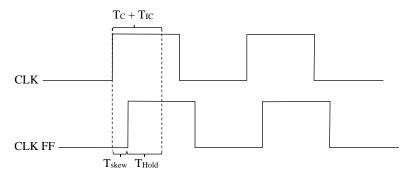

| 3.4.2.Clock Skew                                   | 50 |

| 3.4.3.Setup Slack                                  | 51 |

| 3.4.4.Hold Times                                   | 51 |

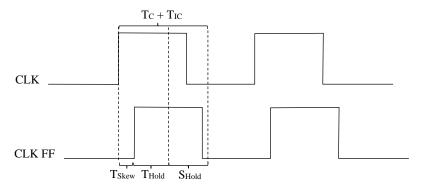

| 3.4.5.Hold Slack                                   | 52 |

| 3.5. Timing optimization methodology               | 52 |

|----------------------------------------------------|----|

| 3.5.1.Logic delays optimization                    | 53 |

| 3.5.2.Interconnect delays                          | 57 |

| 3.5.3.Routing Congestion in FPGA Designs           | 59 |

| 3.5.4.Optimizing Fanout                            | 60 |

| Chapter 4. Efficient AES implementation using FPGA | 62 |

| 4.1. Introduction                                  | 62 |

| 4.2. Motivation for the Proposed Approach          | 62 |

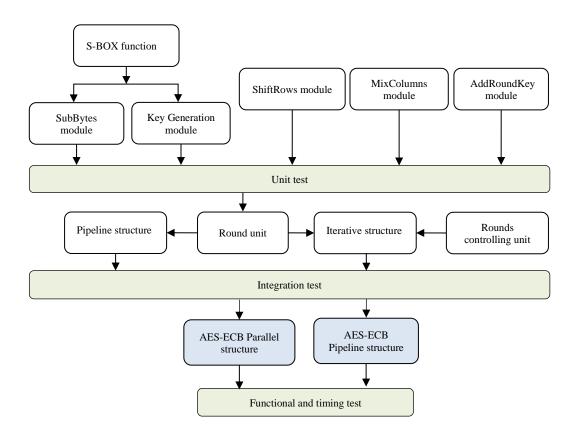

| 4.3. Development process                           | 66 |

| 4.4. Development of different modules              | 66 |

| 4.4.1.SubBytes unit                                | 66 |

| 4.4.2.Key Generation (Key expansion)               | 67 |

| 4.4.3.ShiftRows                                    | 68 |

| 4.4.4.MixColumns                                   | 68 |

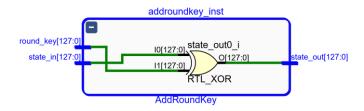

| 4.4.5.AddRoundKey                                  | 69 |

| 4.4.6.Round units                                  | 69 |

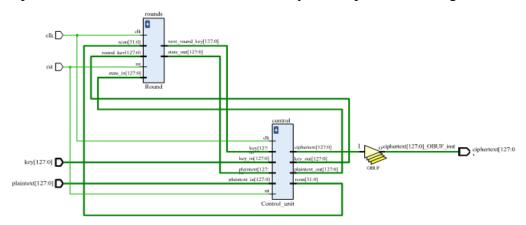

| 4.4.7.Iterations control unit                      | 70 |

| 4.4.8.Design of the iterative system               | 70 |

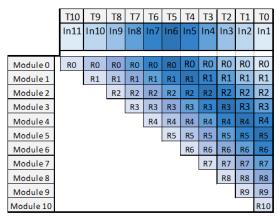

| 4.4.9.Design of the pipeline system                | 70 |

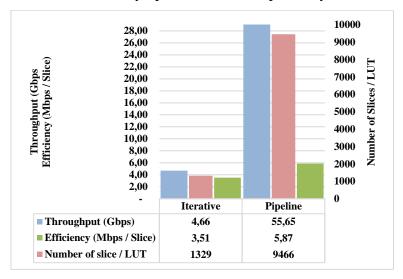

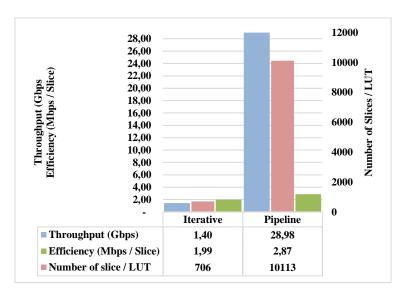

| 4.5. Results and discussion                        | 71 |

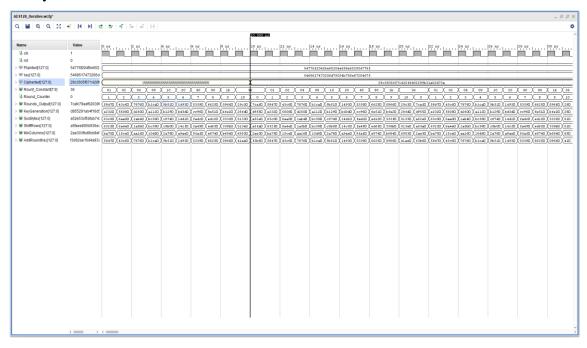

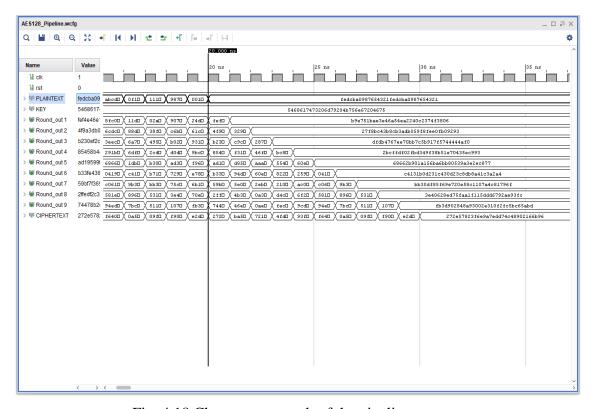

| 4.6. Simulation results.                           | 73 |

| 4.7. Implementation results                        | 74 |

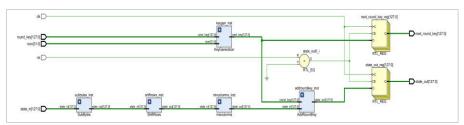

| 4.8. Design of Electronic codebook mode            | 76 |

| 4.9. System Integration                            | 78 |

| 4.10. Conclusion                                   | 79 |

| General conclusion                                 | 80 |

| Reference List                                     | 81 |

# **List of Figures**

| Fig. | 1.1. Simple FPGA architecture                          | 11 |

|------|--------------------------------------------------------|----|

| Fig. | 1.2. AES process of a single plaintext.                | 12 |

| Fig. | 1.3. Operational time rate in AES                      | 12 |

| Fig. | 1.4. Chronogram of pipeline implementation.            | 13 |

| Fig. | 2.1. Security Y-Diagram.                               | 17 |

| Fig. | 2.2 Caesar shift cipher.                               | 19 |

| Fig. | 2.3 Polyalphabetic Substitution Cipher.                | 20 |

| Fig. | 2.4 Example of Hashing.                                | 20 |

| Fig. | 2.5 Symmetric encryption.                              | 21 |

| Fig. | 2.6 DES Encryption algorithm.                          | 22 |

| Fig. | 2.7 Key generation process of DES algorithm.           | 23 |

| Fig. | 2.8 The Feistel function in DES algorithm.             | 24 |

| Fig. | 2.9 Triple DES Algorithm.                              | 24 |

| Fig. | 2.10 AES-128 Algorithm process.                        | 27 |

| Fig. | 2.11 SubBytes operation in AES algorithm               | 28 |

| Fig. | 2.12 MixColumns operation.                             | 30 |

| Fig. | 2.13 Key generation process in AES algorithm           | 31 |

| Fig. | 2.14 Message Authentication Code.                      | 32 |

| Fig. | 2.15 Pseudo Random Function diagram.                   | 33 |

| Fig. | 2.16 Keys use in asymmetric cryptography.              | 35 |

| Fig. | 2.17 Overall asymmetric algorithm process.             | 35 |

| Fig. | 2.18 RSA algorithm flowchart.                          | 37 |

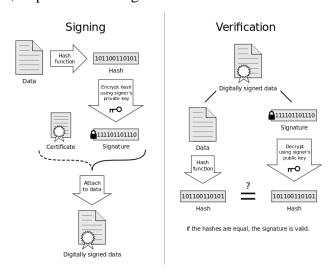

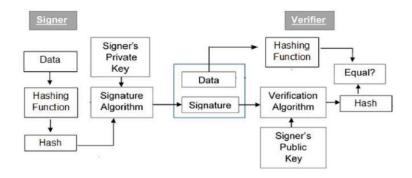

| Fig. | 2.19 Signature creation using RSA.                     | 39 |

| Fig. | 2.20 RSA signature creation and verification process.  | 39 |

| Fig. | 2.21 DSA Signature creation and verification.          | 40 |

| Fig. | 2.22 Electronic Code Book mode (ECB).                  | 41 |

| Fig. | 2.23 Cipher Block Chaining mode (CBC)                  | 42 |

|      | 2.24 Cipher FeedBack mode (CFB).                       |    |

| Fig. | 2.25 Output feedback mode (OFB).                       | 43 |

| Fig. | 2.26 Counter mode (CTR)                                | 45 |

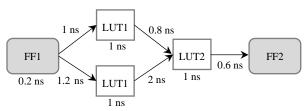

| _    | 3.1 FF to FF timing.                                   |    |

| _    | 3.2 Interconnect delay, and FF delay.                  |    |

| _    | 3.3 Multiple paths for the same destination and source |    |

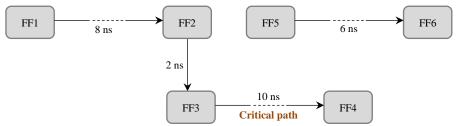

| Fig. | 3.4 Critical path of a design.                         | 49 |

| _    | 3.5 Setup time.                                        |    |

| Fig. | 3.6 clock skew in FPGA circuit.                        | 50 |

| _    | 3.7 Setup slack in FPGA design.                        |    |

| _    | 3.8 Hold time in FPGA circuit.                         |    |

| _    | 3.9 Hold Slack in FPGA design.                         |    |

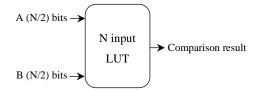

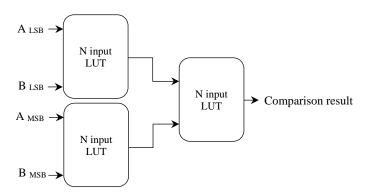

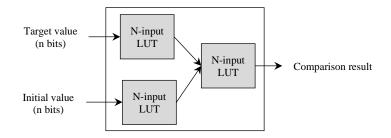

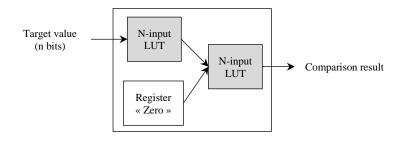

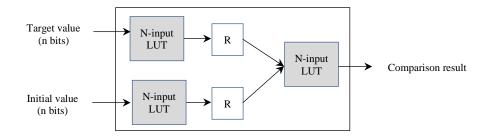

| _    | 3.10 Comparison of N/2-bit vectors.                    |    |

| _    | 3.11 Comparison of N bit vectors.                      |    |

| Fio  | 3.12 Counter design before optimization (counting up)  | 54 |

| Fig. 3.13 Counter design after optimization (counting down)                       | 54 |

|-----------------------------------------------------------------------------------|----|

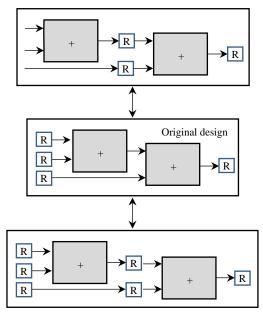

| Fig. 3.14 Pipeline structure in FPGA design.                                      | 55 |

| Fig. 3.15 FPGA design retiming example                                            | 55 |

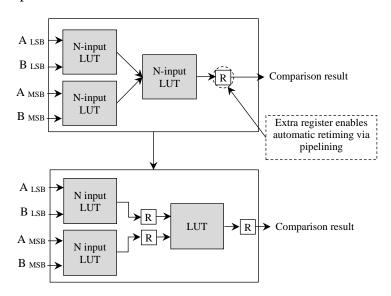

| Fig. 3.16 Simplified pipeline design using automatic retiming: comparator example | 56 |

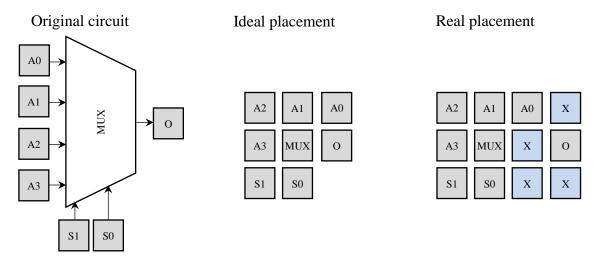

| Fig. 3.17 Interconnect delays: ideal and suboptimal placement.                    | 57 |

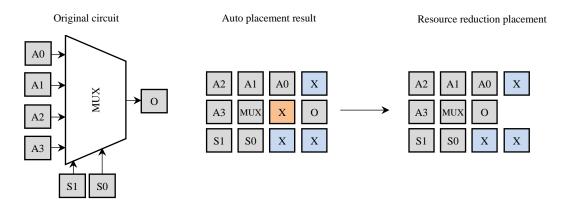

| Fig. 3.18 Resource reduction for a reduced interconnect delay                     | 58 |

| Fig. 3.19 Pipelining long interconnect paths for delay optimization.              | 59 |

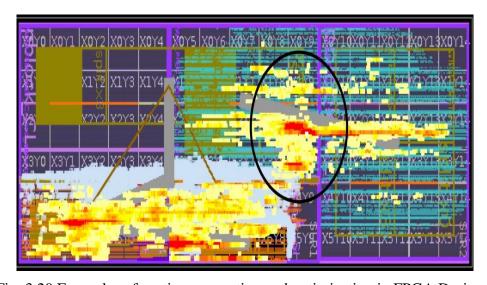

| Fig. 3.20 Examples of routing congestion and optimization in FPGA Designs         | 59 |

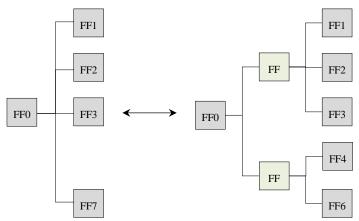

| Fig. 3.21 Register Duplication for Reducing Fan-Out and Routing Congestion        | 60 |

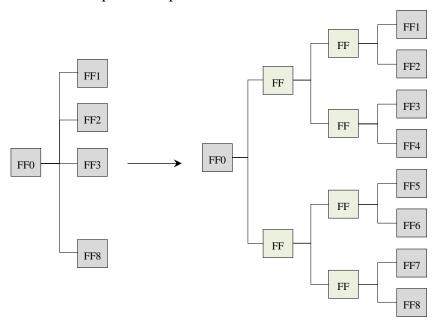

| Fig. 3.22 Pipelining strategy for high fan-out                                    | 61 |

| Fig. 4.1 Encryption process flowchart of the AES algorithm.                       | 64 |

| Fig. 4.2 Iterative architecture process.                                          | 64 |

| Fig. 4.3 Pipeline Architecture of AES algorithm.                                  | 65 |

| Fig. 4.4 Pipeline process of AES algorithm.                                       | 65 |

| Fig. 4.5 Development process of the proposed designs.                             | 66 |

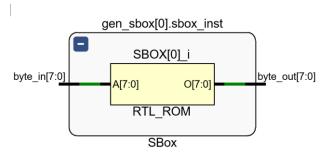

| Fig. 4.6 S-box byte-cell schematic diagram.                                       | 67 |

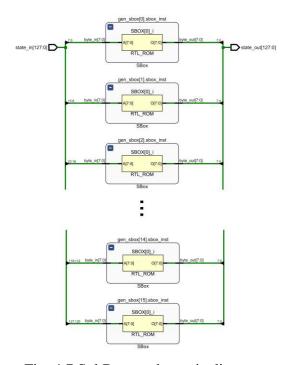

| Fig. 4.7 SubBytes schematic diagram.                                              | 67 |

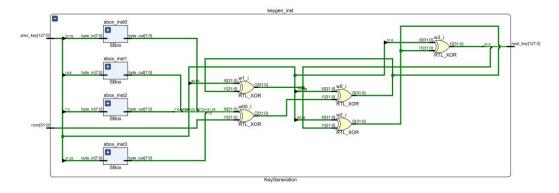

| Fig. 4.8 Key Expansion module schematic diagram.                                  | 68 |

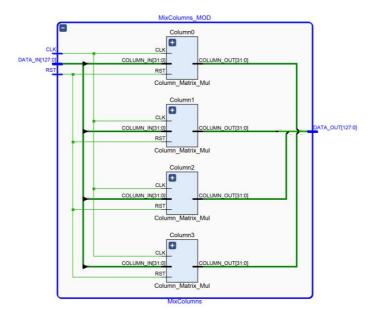

| Fig. 4.9 MixColumns schematic diagram.                                            | 68 |

| Fig. 4.10 MixColumns Sub-Module.                                                  | 69 |

| Fig. 4.11 AddRoundKey schematic diagram.                                          | 69 |

| Fig. 4.12 Schematic diagram of the round unit.                                    | 69 |

| Fig. 4.13 The iterative system schematic diagram.                                 | 70 |

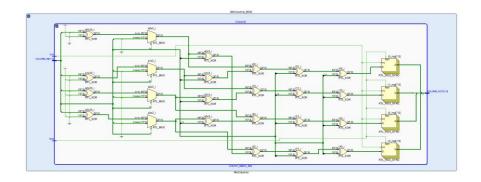

| Fig. 4.14 Pipeline system schematic.                                              | 70 |

| Fig. 4.15 Graphical representation of implementation results in Virtex-7 FPGA     | 71 |

| Fig. 4.16 Graphical representation of implementation results in Zynq7000 FPGA     | 71 |

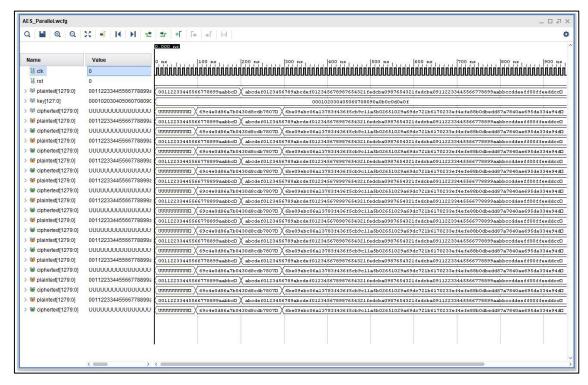

| Fig. 4.17 Chronogram result of the iterative system.                              | 73 |

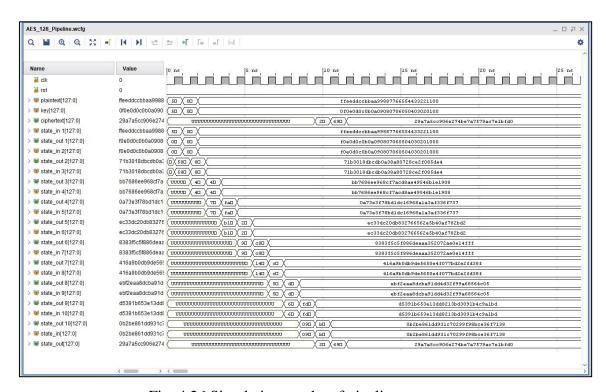

| Fig. 4.18 Chronogram result of the pipeline system.                               | 73 |

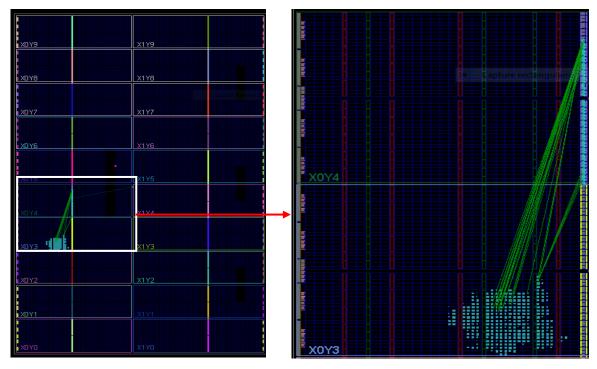

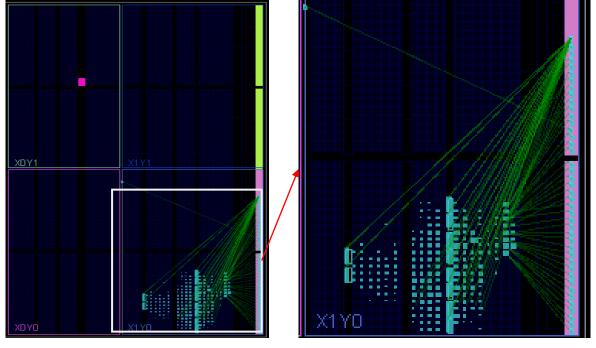

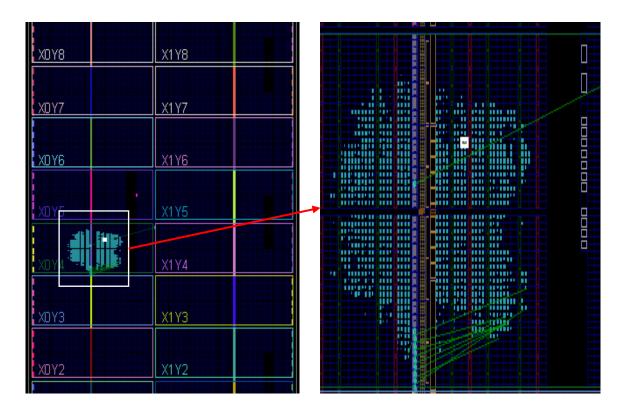

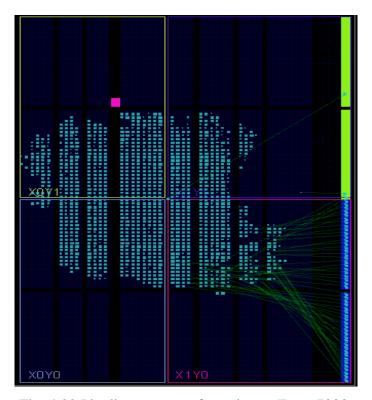

| Fig. 4.19 Implementation footprint of iterative system on Virtex-7 FPGA           | 74 |

| Fig. 4.20 iterative structure footprint on Zynq7000.                              | 74 |

| Fig. 4.21 Pipeline structure footprint on Virtex-7.                               | 75 |

| Fig. 4.22 Pipeline structure footprint on Zynq-7000.                              | 75 |

| Fig. 4.23 Pipeline structure of AES-ECB mode.                                     | 76 |

| Fig. 4.24 Parallel structure of AES-ECB mode.                                     | 76 |

| Fig. 4.25 Simulation results of parallel structure.                               | 77 |

| Fig. 4.26 Simulation results of pipeline structure.                               |    |

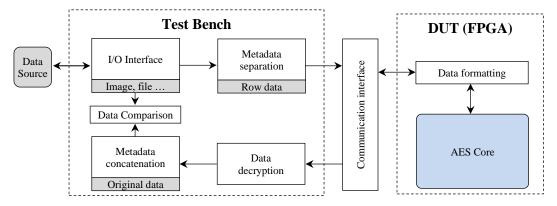

| Fig. 4.27 FPGA In The Loop diagram                                                | 78 |

| Fig. 4.28 System Integration of the proposed security core.                       | 78 |

# **List of Tables**

| Table 3.1. Commonly used hash algorithms                                         | 21 |

|----------------------------------------------------------------------------------|----|

| Table 3.2. Some commonly used algorithms                                         | 21 |

| Table 3.3. Commonly used standards for message integrity                         | 33 |

| Table 3.4. Asymmetric cryptography algorithms                                    | 35 |

| Table 4.1. Protection Mechanisms for some FPGA vendors.                          | 63 |

| Table 5.2. Comparison of the proposed architectures results with published works | 72 |

#### Acknowledgements

I would like to express my deepest gratitude to my supervisors, Pr Hamimi CHEMALI, and Pr Mouloud AYAD, for their invaluable guidance, continuous support, and encouragement throughout my research journey. Their expertise and insightful advice have greatly contributed to the completion of this work.

I extend my sincere thanks to the members of the examination committee, Pr Hamida Abdelhak FERHAT (University of Setif 1), Pr Abdelhalim MAYOUF (University of Setif 1), Pr Abdelhamid DAAMOUCHE (University of Boumerdes), and Pr Abdullatif KHELIL (University of El Oued), for their valuable time, constructive feedback, and thoughtful suggestions, which have significantly improved the quality of this thesis.

My appreciation also goes to Ferhat Abbas University of Setif1 and LCCNS laboratory for providing the necessary resources, facilities, and a stimulating research environment that have been instrumental in the successful completion of my PhD project.

Finally, I would like to express my heartfelt thanks to Dr Salaheddine LAIB and Mr Zinedine MENNANI for their generous help, insightful discussions, and encouragement, which have greatly enriched my research experience.

My gratitude to all those who have contributed to this work in various ways, including friends, colleagues, and family members, for their unwavering support, encouragement, and assistance throughout this journey.

#### **Dedication**

To my dear parents,

whose constant love, countless sacrifices, and endless wisdom have shaped who I am today. Your support has guided me, and your faith in me has been my greatest strength.

To my beloved wife,

my companion through every challenge and success. Your patience, support, and steady belief have been my comfort throughout this journey. Thank you for being by my side every step of the way.

To my wonderful children,

who fill my life with inspiration and happiness. Your bright smiles and endless curiosity remind me daily of the joy of learning.

To my whole family, this work is dedicated to you all, with heartfelt love and gratitude

# **General introduction**

An embedded system is a microcontroller or microprocessor-based system, designed to perform a specific task, either independently or as part of a larger system. It typically consists of two main components: hardware and software, serving as the core intelligence of electronic systems and playing a crucial role in various aspects of daily life. With ongoing technological advancements, embedded systems are playing an increasingly vital role in decision-making. Their importance continues to grow, particularly in smart and cloud-based applications like IoT solutions, where realtime data processing and automation are essential [1]. Numerous areas rely on embedded systems, such as defense, banking, healthcare, and other critical fields, where even a slight security failure may lead to catastrophic consequences for individuals [2]. One example of security failure is the recent remote cyberattack targeting embedded systems in some wireless communication devices, causing widespread disruption, and physical harm to numerous individuals. A similar cyber operation was performed remotely to attack electronic systems that are embedded in a highly sensitive facility, causing significant damage to instruments, and leading to a major failure in the system. These incidents and others highlight the critical risks of an inadequate or insufficient security, where vulnerabilities can be exploited with devastating consequences, which underscores the urgent need for robust security measures to protect systems and safeguard lives [3]. Security measures in embedded systems must address diverse threats, including physical tampering, side-channel attacks, malware, and communication interception. However, the implementation of robust security mechanisms, which usually require high computational capabilities and significant energy within a constrained systems is a difficult operation [4]. Scientists and researchers have thoroughly focused on this challenge, leading to the creation of practical solutions that successfully balance the need for security with the inherent limitations of embedded systems.

This thesis focuses on data security as a critical aspect, emphasizing its role in preventing unauthorized access to sensitive information, or injecting unwanted data, either during a run-time, during data transfer, or a storage operation. Among all security levels, this thesis focuses on data encryption, with a general overview of other security aspects. The research studies the implementation of data security within embedded systems and the challenges associated to it. The practical side of this project aims to the identification of the optimal trade-off between embedding security and maintaining systems' performance through smooth data processing. In this project, an FPGA implementation of the well-known Advanced Encryption Standard (AES) algorithm is elaborated using different structures, to address embedded systems constraints; with a main challenge of preserving the original algorithm without modifications [6].

The development process includes several stages: design, optimization, unit testing, integrity testing of individual modules, and finally, simulation of the overall system. Resource utilization and timing performance form a monitoring parameter along with the efficiency ratio. This comparative analysis highlights the effectiveness of the proposed approaches in balancing between security and efficiency. The remainder of this thesis is structured as follows: Chapter 1 presents a comprehensive literature review of related works and proposed solutions in the field. Chapter 2 provides a foundational background on cryptography, security algorithms, and their practical use cases. Chapter 3 examines common optimization techniques for FPGA designs. Finally, Chapter 4 details the methodology of the proposed project, employing various implementation techniques, and includes an in-depth discussion and analysis of obtained results.

# **Chapter 1. Literature Review**

Embedded systems are fundamental to modern technology, serving as critical components in a diverse array of applications, ranging from consumer electronics to essential infrastructure systems. However, as the complexity of these systems continues to grow, so too do the challenges associated with their design and implementation. Among the most pressing challenges is the need to ensure robust security without compromising performance or efficiency. This chapter presents a comprehensive literature review of the challenges related to integrating security mechanisms into embedded systems, exploring the inherent trade-offs between security, performance, and resource constraints. Additionally, it examines the various solutions proposed in this context, highlighting innovative approaches and methodologies that aim to address these challenges while maintaining the efficiency and reliability of embedded systems.

# 1.1. Limitations and challenge

Embedded systems face a major challenge when integrating additional safety measures, mainly due to their strict constraints on time, resources and performance. These systems often depend on precise process control with minimal latency. Accordingly, the introduction of addition security mechanisms, such as encryption or secure boot processes, leads usually to a latency in processing, which can be considerable in some timing-critical applications [1].

Closely related to timing, the challenge of resource management is equally crucial. Embedded systems generally operate in a limited resource environment, namely, constrained area on hardware chips, or computational power, which require some optimization strategies to bypass this limitation. Which is opposed to security cores that usually require dedicated resource allocation, with some high capabilities and an extended power need. This challenge has attracted the attention of researchers and developers to adopt effective resource management techniques, and ensure that the integration of security functionalities does not degrade overall performance [1]. While enhancing security is essential, the additional layers it introduces can slow down the system, particularly in real-time applications. For instance, implementing secure boot processes in a smart appliance may improve security but could also lead to longer boot times, negatively impacting user experience. This trade-off necessitates careful evaluation during the design phase, to ensure that security measures do not undermine the system's efficiency. Developers must strike a delicate balance between robust security and optimal performance to meet the demands of real-time applications [2].

Beyond these technical challenges, scalability and integration pose additional complexities, especially as embedded systems are deployed across diverse applications such as IoT devices. This requires adaptable and scalable solutions that can accommodate the unique demands of different environments without compromising security or functionality.

In summary, integrating security into embedded systems involves navigating a complex landscape of challenges, including timing constraints, resource limitations, performance trade-offs, and scalability issues. Addressing these challenges requires a complete approach that combines thoughtful design, optimization, and a deep understanding of the interplay between security and system constraints. By carefully considering these factors, developers can create embedded systems that are not only secure but also reliable and high-performing.

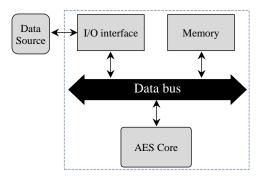

# 1.2. Implementation of cryptographic algorithms

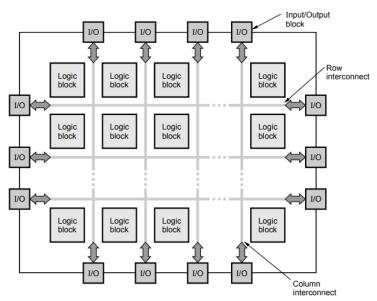

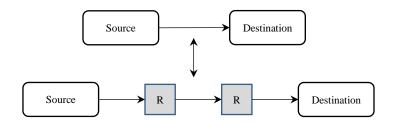

Field Programmable Gate Arrays (FPGA) are an ideal platform for embedded system developers, offering the flexibility to redesign and describe desired architectures using a high-level language. FPGA is an integrated circuit or chip that enables the creation of fully customized digital logic. It consists of numerous logic cells that serve as the fundamental building blocks for designing digital circuits. These cells can be configured to operate in specific ways by interconnecting them and optimizing their functionality to form the core of any digital circuit. Additionally, FPGAs provide access to various resources, such as clock signals, RAM blocks, and interfaces for managing different types of inputs. Some advanced FPGAs include also peripherals like analog-to-digital converters and analog outputs. One of the key advantages of FPGAs is the ability to support parallel processing, allowing multiple operations to execute within a single clock cycle. A simple architecture of FPGA is represented in Fig. 1.1.

Fig. 1.1. Simple FPGA architecture.

Implementing cryptography and encryption algorithms in embedded systems presents significant challenges due to the complexity of the mathematical operations involved. These algorithms often require extended processing times because of their recursive nature, which can strain the limited computational resources of embedded systems. Compounding this challenge is the fact that data

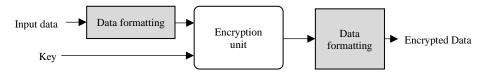

encryption in such systems is typically a secondary task, operating quietly in the background without disrupting primary functions. To address this, the encryption unit is often integrated as a black box, designed to process input data and produce output as efficiently and seamlessly as possible.

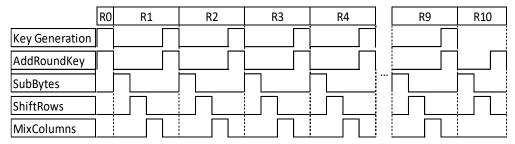

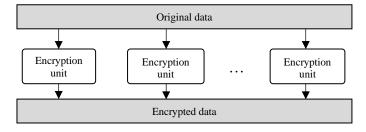

A prime example of this complexity is the Advanced Encryption Standard (AES), a widely used encryption algorithm. The processing time of AES depends on rounds, which are iterative sets of operations executed sequentially. In this structure, the output of one function serves as the input to the next, creating a recursive sequence that is repeated N times based on the key length. This design introduces latency, as each processing unit remains idle while waiting for input from the previous operation. As illustrated in Fig. 1.2, the chronogram of an AES encryption process reveals that the holding time, which is defined by the period during which units wait for input, is considerable. When analyzing the rate of processing time relative to total time in an iterative AES design, the latency becomes even more apparent, highlighting the need for optimization in embedded systems where efficiency is critical.

Fig. 1.2. AES process of a single plaintext.

The chronogram demonstrates that only one in four operations is executed each time, resulting to an operational rate of R = 24%, which signifies a 76% of holding time as shown in Fig. 1.3.

Fig. 1.3. Operational time rate in AES.

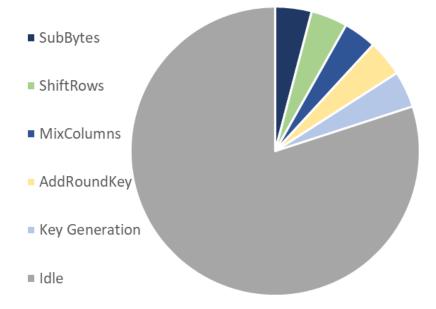

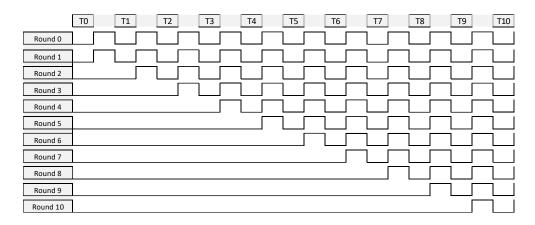

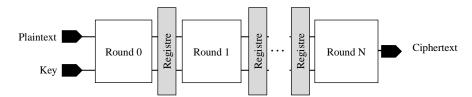

In contrast, the pipeline implementation of the AES divides the encryption process into multiple stages that operate concurrently. This parallelism allows each stage to process data independently, eliminating the idle waiting time and enabling a continuous flow of operations. As shown in Fig. 1.4, the chronogram of the pipeline approach demonstrates a high reduction in holding time, leading to a faster and more efficient encryption process. The throughput of the system increases significantly, as data moves seamlessly through the pipeline without the bottlenecks inherent in the traditional method.

Fig. 1.4. Chronogram of pipeline implementation.

The chronogram in Fig. 1.4 clearly shows that the operational rate, defined as the ratio of active processing modules to holding modules, is approximately 50% for the first input. Since each module performs a single round, the first module becomes available to process the next plaintext immediately after completing the current one. Additionally, the operational rate reaches 100% after 10 ciphertexts with a steady data flow.

The key takeaway that we conclude from the comparison made above, is the profound impact that the choice of implementation method has on the overall performance of cryptographic algorithms in embedded systems. By carefully selecting and optimizing the implementation approach (whether iterative, pipeline, or another technique) designers can significantly enhance processing speed, reduce latency, and improve resource utilization. The implementation technique is not the only method to enhance performance, other techniques are thoroughly described in literature, addressing the efficiency of the implementation of cryptography algorithms in hardware and software. The following section enumerates some of recent works on this field.

#### 1.3. Related works

The growing demand for secure and efficient embedded systems has driven researchers to explore various techniques for optimizing security cores, particularly in the context of cryptography and encryption. As embedded systems often operate under stringent constraints, such as limited computational power, memory, and energy resources, traditional cryptographic algorithms and their

implementations may not always be suitable. To address these challenges, researchers have proposed a wide range of optimization strategies, each targeting different aspects of the design and execution of security cores. This section provides a comprehensive overview of these optimization techniques, categorized based on the type of modification they introduce.

# 1.3.1. New lightweight block ciphers

Several approaches are proposed in literature to propose new lightweight block ciphers. Authors in [3], developed a lightweight block cipher, the proposed algorithm was examined to test its efficiency, where it acquires a good level of cryptographic characteristics, and a crypto analyses was performed to test security. The algorithm is derived from the WG stream cipher. The proposed algorithm was implemented in a low-power MCU to evaluate its performance and compared with other similar works. The contribution of this work was on the power consumption which represents a major limitation in embedded systems. This proposed cipher was designed for energy-constraint systems, especially those powered from an external source such as RFID tags, smart cards, wireless sensors etc.

In [4], authors designed a combination of Feistel and ARX structures to develop a new block cipher GFRX for resources-limited systems. The proposed algorithm intervenes in the round function by reducing complex operations, and take advantage of the flexible combination of Feistel and ARX to resolve the diffusion and confusion latency in traditional structures. This project shows better results compared to ARX and Feistel separated. It was tested against effective differential and linear attacks, and therefore is considered secure.

Yan et al in [5], suggested a new dynamic S-box based block cipher DBST, this new approach is based on bit-slice technology, where the s-box depends on the key. This new approach increases randomness, and enhance security against differential and linear attacks. The rounds operation is based on a new Feistel variant structure, and shows more infusibility compared to traditional structure. The authors compared their work to similar lightweight algorithms, and concluded that it is well adapted for 5G applications.

Authors in [6], investigated a new block cipher RAZOR designed for IoT application. The new approach is aimed to enhance security, but also to be resource-efficient for resource-limited systems. The diffusion layer is based on XOR operations and rotation, the project was implemented in software. Security analyses is proven against both differential and linear attacks. RAZOR was compared with other similar algorithms in terms of security.

A lightweight crypto algorithm named LBC-IoT is proposed in [7]. The objective of the project is to design a security-enhanced algorithm adapted to resource-limited systems. LBC-IoT uses a compact s-box. The advantage of the proposed algorithm is its simplicity, and the low GE it has compared to

similar works. Additionally, it is well adapted to resource-limited devices as it has a small software footprint.

Buja et al in [8] presented a survey on lightweight ciphers for mobile big data computing. The study addresses data security concerns on mobile, and concluded that existing lightweight algorithms have some issue that should be taken in consideration. The necessity to develop data security algorithms for resource-limited systems, and the drive to propose compact algorithms should never come at the expense of ignoring or downplaying security concerns. The advancement of computer calculation capacities accelerates the attacks technique and put current data security systems into danger, which requires finding new solution, or enhancing existing methods.

# 1.3.2. Lightweight hash functions

Hash functions have also been a significant focus of research, particularly in optimizing their efficiency and security for resource-constrained embedded systems. Andrey et al, proposed in [9] a lightweight Hash function named SPONGENT. The new function supports 88, 128, 160, 224, and 256 bits. This function has a small footprint, compared to similar functions, while for throughput and area requirement, they depend on the technology used.

In [10], Susila et al, presented an implementation of a lightweight hash functions LWCHF. The proposed implementation is done in hardware and software, and results were examined based on nine metrics. The cost of the final solution, and the security against different attacks, in addition to performance were considered in the development process.

Sevin and Çavuşoğlu in [11], proposed a new lightweight hash based on encryption algorithm. The efficiency of proposed system was examined, and security performance was carried out and detailed in the study. The algorithm shows a robustness against differential and linear attacks, and sensitivity of hash value analyses showed a high precision for all cases.

Jian, Thomas and Axel in [12], proposed PHOTON, based on a well-known AES design strategy, with the introduction of a new layer without affecting its size, to make fit small area devices. The proposed approach attained an excellent area / throughput trade-off.

# 1.3.3. Implementation optimization

Another optimization approach focuses on enhancing the implementation technique of the algorithm itself, without making adjustments to its core structure. A pipeline and parallel implementation of the AES is presented by Nabil et al in [13]. The aim of this research is the reduction of processing time. The idea was to use maximum resources available in the design, and eliminate idle time. Results are compared to traditional implementation method proposed by them, and also compared to software

implementation and similar hardware approaches, in terms of resources and timing performance. The parallel architecture achieved the highest throughput at the cost of increased resource utilization.

A hybrid pipeline architecture was proposed in [14] by Algredo-Badillo et al. The proposed architecture combines time redundancy and hardware redundancy, and results show an enhanced resource utilization compared to standard AES. The designed system is based on error detection to avoid cascade effect, and it is well adapted to IoT systems.

In [15], P Rajasekar and H. Mangalam proposed an area optimized and power efficient AES implementation in FPGA for IoT applications. This proposed approach addresses issues related to power consumption and area, to design and implement optimized functions for AES core. Simulation results show that the proposed architecture provides high security with low power, and reaches a maximum frequency of 190 MHz.

Authors in [16] propose a low area high-speed FPGA implementation of the AES architecture for cryptography applications. It introduces a modified positive polarity reed muller (MPPRM) architecture for the SubBytes and InvSubBytes transformations to reduce hardware requirements and improve speed.

In [17], S. J. H. Pirzada et al describe an optimization proposition of the AES algorithm for satellite applications. This proposed optimization is adapted to the space environment. Implementation results are presented in details, with a security analysis against recent attacks.

## 1.4. Conclusion

Advancements in cybersecurity demand the enhancement of security algorithms, resulting in more complex mathematical operations and arithmetic functions. This, in turn, requires greater energy, resources, and processing time; further emphasizing the challenges of constrained systems, and making the integration of security solutions into embedded systems a challenging task.

In summarize, it is noticeable when looking to proposed solution that there are two major axes of cryptography algorithms optimization for embedded systems. The first intervene on the algorithm itself, via proposing new block cipher algorithms, combining several methods or applying some adjustments on existing approaches. The second preserves the original algorithm without any adjustments, but focus on implementation technique, via introducing parallelism to the design, implement pipeline stages, or switching between implementation methods such as logic-based, memory-based or hybrid implementation. The distinction between these approaches lies in the validation phase. Where methods that involve modifying existing algorithms or proposing new ones require additional security analyses to demonstrate the robustness and reliability of their approach against various attacks and threats.

# **Chapter 2. Theoretical Background on Cryptography**

# 2.1. Introduction

The written word stands as one of humanity's most transformative inventions, it enables the sharing and preservation of knowledge across generations. With the presence of the ability to communicate, came the equally the important need to protect sensitive information from unintended eyes. This dual necessity to share and to conceal, has driven the evolution of cryptography, a field dedicated to securing information through encoding and decoding techniques. From ancient ciphers to modern encryption algorithms, cryptography has played an important role in safeguarding communication, ensuring privacy, and enabling trust in an increasingly interconnected world. This chapter explores the foundational concepts and historical development of cryptography, providing the essential background for understanding its critical role in today's digital age.

# 2.2. Core Security Principles

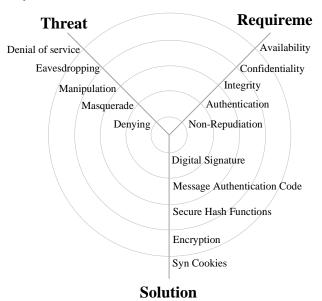

The fundamental aspects of security provide a solid framework for protecting embedded systems and digital technologies. These principles ensure the protection of data and system integrity, enabling trusted operations in increasingly connected environments. By addressing confidentiality, integrity, authentication, they offer a comprehensive approach to mitigating security risks. Each system that deals with data transferring or data storage have this compromise of three characteristics to guarantee a good level of security [18]. The balance between these characteristics varies depending on the field of application of that system. Core Security principles and threats with corresponding solutions are illustrated in Fig. 2.1, as designed by Shoufan and Huss in [19]. The diagram shows the level of intervention for each security concern and the dedicated solution.

Fig. 2.1. Security Y-Diagram.

# 2.2.1. Confidentiality

Confidentiality is the principle of ensuring that sensitive information is accessible only to authorized individuals or systems. For embedded systems, this may involve encrypting data stored in memory, transmitted over networks, or processed within the device. Confidentiality is crucial in applications like IoT, where devices usually handle personal or private information. For example, a smart home system must ensure that communication between sensors and the central controller remains private to prevent unauthorized access.

Embedded systems achieve confidentiality through cryptographic methods such as symmetric encryption (e.g. AES) and asymmetric encryption (e.g. RSA). However, implementing these methods in resource-constrained devices can be challenging. Hardware accelerators, including FPGAs, are often used to optimize encryption processes while maintaining high performance [20].

# 2.2.2. Integrity

Integrity ensures that data remains unaltered during storage, processing, and transmission, barring any unauthorized changes. In embedded systems, this principle is critical for maintaining the reliability and accuracy of operations. For instance, in automotive systems, ensuring the integrity of control signals between the vehicle's sensors and actuators is essential for safety.

To safeguard integrity, embedded systems employ techniques like checksums, cryptographic hash functions, and digital signatures. These mechanisms verify that data has not been tampered with, whether due to accidental corruption or malicious attacks. Secure firmware updates are another critical aspect, ensuring that only authentic and verified software runs on the device [21].

# 2.2.3. Availability

Availability refers to ensuring that a system remains operational and accessible to authorized users whenever needed. This principle is especially vital for embedded systems in critical applications, such as medical devices or industrial control systems, where downtime could lead to severe consequences [22].

Threats to availability include denial-of-service (DoS) attacks, hardware failures, and resource exhaustion. Embedded systems mitigate these risks through redundancy, fault-tolerant designs, and real-time monitoring. For instance, a pacemaker must remain available under all circumstances to sustain a patient's life. In such cases, embedded systems incorporate backup components and failover mechanisms to ensure uninterrupted operation.

### 2.2.4. Authentication

Authentication is the process of verifying the identity of users, devices, or systems before granting access to resources. In embedded systems, authentication is a cornerstone of secure communication and operation. For example, in IoT networks, devices must authenticate themselves to a central hub to establish trusted communication channels.

Authentication mechanisms include passwords, digital certificates, and biometric verification. Embedded systems often use lightweight authentication protocols, such as HMAC or public-key infrastructure (PKI), tailored to their resource constraints. Secure boot processes also rely on authentication to ensure that only trusted firmware is executed, protecting the system from malicious code [23].

# 2.3. Cryptography

The word cryptography comes from the Greek meaning "hidden writing". Some of the earliest forms of secret writing come from ancient Greece as well, where military used a covered letters that are written in a wooden board on what is known as "steganography" which means a covered writing. This approach has some issues, the main one is that once the message is discovered, its contents will be easily revealed. This dilemma gave rise to "cryptography" which doesn't hide the existence of a message but instead hides its meaning.

Cryptography can be broken down into two subtypes: transposition and substitution. Transposition is when a document is rearranged creating an anagram, which is the earlier form of cryptography. An early historical example is once again from ancient Greece, where they used military method of communications, consists of wrapping the message around a wooden rod, in a way that it can't be read unless it is wrapped again around an identical rod, otherwise the message would seem like jumble of letter. This method has its limitations, especially when dealing with large messages.

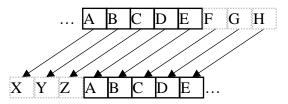

Because of the limitations in the transposition cryptography, the substitution cryptography was created. Substitution replaces the letters of a message rather than rearranging them. The most famous substitution cipher is the Caesar cipher, also known as the Caesar shift cipher as illustrated in Fig. 2.2, where it replaces any given letter with another letter from the alphabet (shift over a given offset) [24].

Fig. 2.2 Caesar shift cipher.

The only information that keeps the original message secure in the case of shift cipher is the shifting offset value, which is not enough to prevent unauthorized decryption in most cases. Cryptography progressed steadily over time, and hacking techniques were also advancing. Nowadays it includes combinations of complex operations such as characters substitution, data shifting, and mixing with keywords. Fig. 2.3, shows an example of an obsolete substitution cipher (Polyalphabetic Substitution Ciphers).

|        | Α      | В         | С  | D   | F   | F        | G   | Н | 1   | 1    | K   | L    | М      | N      | 0  | Р | Q        | R   | S      | Т        | IJ       | V        | w  | Х        | Υ    | 7        |

|--------|--------|-----------|----|-----|-----|----------|-----|---|-----|------|-----|------|--------|--------|----|---|----------|-----|--------|----------|----------|----------|----|----------|------|----------|

| Α      | A      |           |    | D   | F   |          |     | Н | ÷   | -    | K   | L    |        |        | 0  |   | a        | R   |        | -        | <u> </u> | v        | W  |          | Y    | 7        |

| В      | B      |           |    | F   | F   | G        |     |   |     | K    | L   | М    |        | O      | P  |   | R        | S   |        | Ü        |          | w        | X  | Ŷ        | 7    | Α.       |

| С      | C      | ···       | F  | F   | G   | <u>u</u> |     |   | J.  |      | D.4 | N    | O      |        | 0  | R | S        | - T |        | v        | ļ        | X        | Ŷ  | 7        | ·    | .^.<br>B |

| D      | D      |           |    | G   | Н   | Ψ.       | -   | K |     | М    | N   | O.   | P      | ·      | R  | S | T        | Ü   | v      | ٧,       | X        | ÷        | 7  | A        | سنند | Ĉ        |

| F      | F      | )         | G  |     | *** | +        | K   |   | М   |      | O   | P    | r<br>O |        | S  | T | Ü        | v   | 14/    | X        | Ŷ        | 7        | Δ. | A<br>B   |      | D        |

| F      | F      |           |    |     | +   | K        |     | М |     | 0    | P   | 0    | R      | S      | T  |   | v        | V   | X      | ·        | 7        |          | В  | <u>-</u> | D    | F        |

| -      |        |           |    |     | ,   |          | -   |   |     | P    | 0   |      |        | э<br>Т | U  |   | w        | VV  |        | 7        | ļ        | B        | C  |          | ·    |          |

| G<br>H | G<br>H | · · · · · |    | 'n. | K   | Ļ.       | IVI |   |     | 0    | R   | R    |        | Ü      |    |   |          | X   | 7<br>7 | ·        | ļ.C.     | C        |    | D<br>E   | F    | F<br>G   |

|        |        |           | 1  | K   | ٠.  | M        |     |   |     | - D. |     | 5    |        |        | V  | W | X        | Y   | ۷.     |          | ļ        | <u>.</u> | D  |          |      |          |

| 1      | Щ      |           | K  | Ļ.  | М   |          | 0   | Р | Q   | R    | S   |      | U      | ٧      | W  | X | <u>.</u> | Z   | A      | В        | C        | D        | E. | F        |      | H        |

| J      | J      | ļ         |    | М   | N   | 0        |     | Q | Li. | S    | T   | U    | ٧      | W      | X  | Ψ | Z        | Α   | В      | <u>.</u> | D        | E        | F  | G        | Н    |          |

| K      | K      | ·         |    |     | 0   | Р.       | Q   | R | S   | T    | U   | V    |        | X      | Y  | Z | Α.       | В   | C      | D        |          | F        |    | Н.       |      | 'n.      |

| L      | L      |           |    | 0   | P   | Q        |     | S | Т   | U    | V   | W    | X      | Y      | Z  | A | В        | C   | D      | E        | F        | G        | Н  | 1        | J    | K        |

| М      | M      | سننخ      |    | Р   | Q   | R        |     | Ţ |     | V    | W   | سننا | بننا   |        | Α  |   | c        | D   | E      |          | بتسإ     | Н        | Ш  | J.       | ستنب | ᅹ        |

| Ν      | N      |           | Р. | Q   | R   | S        | T   | U | ٧   |      | X   | Υ    | Z      |        | В  | C | D        | Ε.  | F      | G        | H        | 1        | 1  | K        |      | М        |

| 0      | 0      | ·         |    | R   | S   | Τ.       |     | ٧ |     |      | Υ   | Z    | Α      | ·      | С  | D | Ε.       | F   | G      |          | <u></u>  | J        | K  | L        | М    | N        |

| Р      |        | Q         |    | S   | Т   | <u> </u> | ٧   | W | Х   | Υ    | Z   | Α    | В      | С      | D  |   | F        | G   | Н      | 1        | J        | K        | L  | М        | N    | 0        |

| Q      | Q      | R         | S  | Ţ   | U   | ٧        | W   | Х | Υ   | Z    | Α   | В    | c      | D      | Ε. | F | G        | Н   |        | J        | K        | L        | М  | N        |      | Р        |

| R      | R      |           | T. | U   | ٧   | W        |     | Υ | Z   | Α    | В   | C    | D      | E      | F  | G | Н        |     | J      | K        | L        | М        | N  | 0        | Р    | Q        |

| S      | S      | T         | U  | ٧   | W   | Х        | Υ   | Z | Α   | В    | C   | D    | Ε      | F      | G  | Н | 1.       | J   | K      | L        | М        | N        | 0  | Р        | Q    | R        |

| Т      | Т      | U         | ٧  | W   | Х   | Υ        | Z   | Α | В   | С    | D   | Ε    | F      | G      | Н  | 1 | 1        | K   | L      | М        | Ν        | 0        | Р  | Q        | R    | S        |

| U      | U      | ٧         | W  | Х   | Υ   | Z        | Α   | В | С   | D    | Ε   | F    | G      | Н      | 1  | J | K        | L   | М      | Ν        | 0        | Р        | Q  | R        | S    | Т        |

| ٧      | ٧      | W         | Х  | Υ   | Z   | Α        | В   | С | D   | Ε    | F   | G    | Н      | 1      | J  | K | L        | М   | Ν      | 0        | Р        | Q        | R  | S        | Т    | U        |

| W      | W      | Х         | Υ  | Z   | Α   | В        | С   | D | Ε   | F    | G   | Н    | 1      | J      | Κ  | L | М        | N   | 0      | Р        | Q        | R        | S  | Т        | U    | ٧        |

| Х      | Х      | Υ         | Z  | Α   | В   | С        | D   | Ε | F   | G    | Н   | 1    | J      | K      | L  | М | N        | 0   | Р      | Q        | R        | S        | Т  | U        | ٧    | W        |

| Υ      | Υ      | Z         | Α  | В   | С   | D        | Ε   | F | G   | Н    | 1   | J    | K      | L      | М  | N | 0        | Р   | Q      | R        | S        | Т        | U  | ٧        | W    | х        |

| Z      | Z      | Α         | В  | С   | D   | Ε        | F   | G | Н   | ï    | J   | K    | L      | М      | N  | 0 | Р        | Q   | R      | S        | Т        | U        | ٧  | W        | Χ    | Υ        |

Fig. 2.3 Polyalphabetic Substitution Cipher.

The process of securing data using this set of operation is called Encryption, which is defined as the process of converting plaintext into secure, unreadable data (ciphertext) using specific algorithms.

# 2.4. Hashing and Hashing Algorithms

Hashing or hashing algorithms are mathematical formula, that transform messages into a deterministic fixed length representation of the original string. The result of a hashing algorithm is called the "digest", and this digest is the representational string that represents the original message. A simple example of a hashing algorithm, is the summation of the alphabetic orders of the original message letters, an example is presented in Fig. 2.4.

Fig. 2.4 Example of Hashing.

The purpose of a hashing algorithms, is to determine if the original message has changed since it was last hashed. If word "hello" in the previous example is changed to the word "cello", the same hashing algorithm will result 47 instead of 52. We can easily then tell that the message has been changed by simply comparing the resulting digest. It is impossible to reverse engineer Hash unless the number of

characters of the original message is known. In this case a brute force attack can be applied to get all the possible combinations [25]. Some commonly used hash algorithms are presented in Table 2.1.

Table 2.1. Commonly used hash algorithms

| Legacy | md5, sha1                              |

|--------|----------------------------------------|

| Modern | SHA224, SHA256, SHA384, SHA512         |

| Future | SHA3-224, SHA3-256, SHA3-384, SHA3-512 |

# 2.5. Symmetric cryptography

Symmetric cryptography is mathematical operations that are performed with a secret key, and either verified or undone with the same secret key. Symmetric cryptography includes three operations: encryption, Message Authentication Code (MAC), and pseudo random function [26].

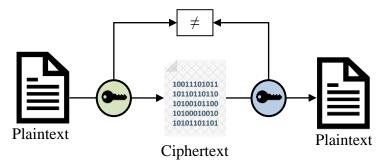

# 2.5.1. Symmetric encryption

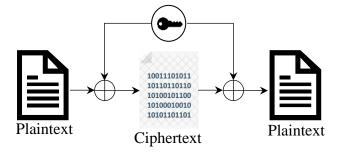

Encryption is a subset of cryptography and involves the process of converting readable data into unreadable. It is needed to protect important information from being accessed by unauthorized parties before transmitting or storing. Encryption uses a secret key, and a specific algorithm to process data, so that it appears as random and incomprehensible as possible.

The word symmetric signifies that the same key is used for encryption and decryption. The simplest example. The symmetric encryption process is shown in Fig. 2.5.

Fig. 2.5 Symmetric encryption.

There are many encryption algorithms, Table 2.2 lists some common algorithms. AES is one of the most famous algorithms.

Table 2.2. Some commonly used algorithms

| Legacy | DES, RC4, 3DES                   |

|--------|----------------------------------|

| Modern | AES-128, AES-192, AES-256        |

| Future | AES (is considered Quantum safe) |

#### 2.5.1.1. Data Encryption Standard algorithm (DES)

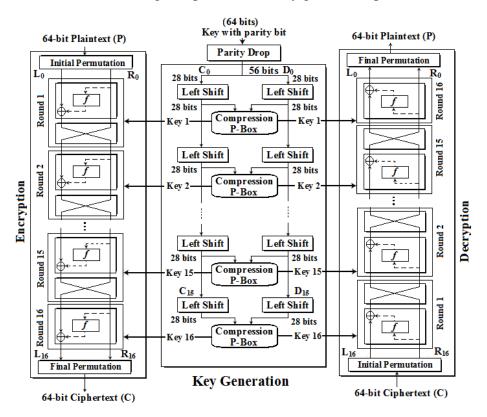

Data encryption standard (DES) is one of popular symmetric encryption algorithms. DES is developed between 1972-1977. It is a block cipher of 64-bit block, and a key length of 56-bit, which means that it processes 64-bits of data at a time. The full Encryption and Decryption process of the DES algorithm is illustrated in Fig. 2.6. The small size of DES key makes it fragile against brute force, a reason that made the algorithm obsolete, and no longer supported. DES is separated into two processes, the key generation known also by Key schedule, and the encryption process.

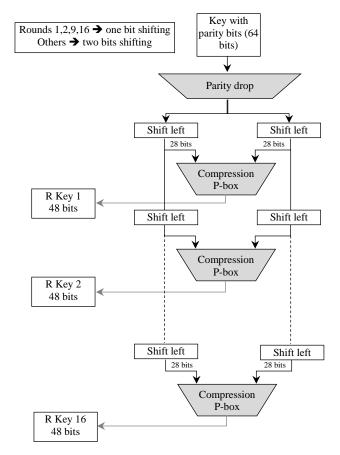

The key generation process, as the name suggests, involves creating subkeys for each round of the encryption process. [27]. The first step in this process is the key selection, where 56-bits are selected from the initial key through the Permuted Choice, which is a table that rearranges the key, and reduces it from 64 bits to 56-bits by discarding the rest (8-bit), which are used as parity bits. the selected bits are split after that into two parts: left and right ( $C_0$  and  $D_0$ ). Each part is shifted cyclically to the left by 1 or 2 positions depending on the round number. Both halves are compressed in the final operation to form a 48-bit key that serves the encryption process as a subkey. The operations described above are repeated for all the 16 rounds. Fig. 2.7 presents the Key generation process of the DES algorithm.

Fig. 2.6 DES Encryption algorithm.

Fig. 2.7 Key generation process of DES algorithm.

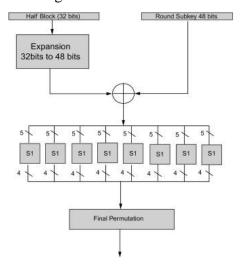

The encryption process on the other hand is a set of operations applied to the plaintext to generate the ciphertext using the provided key. The plaintext passes by the Initial permutation (IP) to reorder all the bits according to a predefined table. The output of the IP is then divided into two parts ( $L_0$  and  $R_0$ ), the size of each is 32 bits. Each half goes through a Feistel Cipher function to perform the 16 rounds as follows:

Input:  $L_{i-1}$  and  $R_{i-1}$  (the left and right 32-bit halves from the previous round).

Process: For each round i (where  $i \in [1, 16]$ )

- Compute the new left half:  $L_i = R_{i-1}$

- Compute the new right half:  $R_i = L_{i-1} \oplus F(R_{i-1}, K_i)$

Where:

- *F* is the Feistel function.

- $K_i$  is the subkey from the key generation process

The Feistel function  $F(R_{i-1}, K_i)$ :

- Expansion (E): The expansion of the 32-bits to 48-bits.

$$E(R_{i-1}) = 48 bit$$

- Key Mixing: The expended 48-bits block is XORed with the 48-bits subkey  $k_i$

$$A = E(R_{i-1}) \oplus k_i$$

- Substitution (S-boxes): The 48-bit result A is divided into 8 groups of 6 bits each. Each group is processed by a corresponding S-box (Substitution box), which reduces the 6 bits to 4 bits. This results in a 32-bit output.

$$B = S_1(A_1) \parallel S_2(A_2) \parallel \cdots \parallel S_8(A_8)$$

- Permutation (P): The 32-bit output *B* is permuted using the Permutation Table (P-table)

$$aF(R_{i-1}, K_i) = P(B)$$

The Feistel function is represented in Fig. 2.8.

Fig. 2.8 The Feistel function in DES algorithm.

#### 2.5.1.2. Triple DES Encryption algorithm

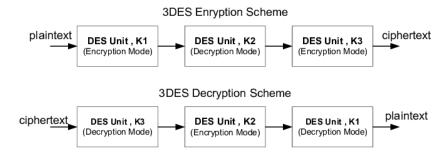

As its name indicates, the Triple DES algorithm is an extended version of the DES algorithm. 3DES uses three different keys to be able to perform its encryption process. It actually performs three separate passes through the data, and that's the signification of number 3 in its name. The first pass encrypts the plaintext with the first key, the second pass decrypts the result with the second key, and the third pass performs an encryption of result with the third key [28]. A presentation of the 3DES algorithm is shown in Fig. 2.9.

Fig. 2.9 Triple DES Algorithm.

#### 2.5.1.3. RC4 Algorithm

RC4 is a stream cipher algorithm, it was created by Ron Rivest as a part of the original web stand, that is no longer used in today wireless networks. it was also a part of the SSL standard, but when replaced by TLS, RC4 was also replaced. One of the major problems in RC4 is the biased output, that means if the third byte of the original state is zero, and the second byte is not equal to two, then the second output byte is always zero. This little quirk that caused the deprecate of use of RC4 making it not a very common symmetric encryption today [29]. The RC4 algorithm is illustrated in Figure 9.

Here's a breakdown of the mathematics behind RC4

The Key Scheduling Algorithm (KSA) initializes the permutation of an array S, based on the input key:

- Initialization of *S*: The array *S* is initialized with values from 0 to 255:

$$S[i] = i, for i = 0,1,...,255$$

- Mixing S using the Key K:

$$j = 0$$

For  $i = 0$  to 255:

$$j = (j + S[i] + K [i \mod len(k)]) \mod 256$$

Swap  $[i] \leftrightarrow S[j]$

Where:

- *K* is (a variable-length key, typically 5 to 256 bytes).

- len(k) is the length of K.

The result is a scrambled array *S* that depends on the input key.

Pseudo-Random Generation Algorithm (PRGA) uses the scrambled *S* array to generate a stream of pseudorandom bytes:

- Initialization

$$i = 0, j = 0$$

- Generate pseudo-random byte: For each iteration

- Increment i  $i = (i + 1) \mod 256$

- Update j  $j = (j + S[i]) \mod 256$

- Swap  $S[i] \leftrightarrow S[j]$

- Generate pseudorandom byte (Output):

$$S[(S[i] + S[j]) \mod 256]$$

RC4 encryption and decryption are performed by XORing each byte of the plaintext or ciphertext with the corresponding byte of the keystream:

- Encryption

$$C[n] = P[n] \oplus K[n]$$

Where:

- C[n] is the  $n^{th}$  byte of the ciphertext.

- P[n] is the  $n^{th}$  byte of the plaintext.

- K[n] is the  $n^{th}$  byte of the keystream.

- Decryption

$$P[n] = C[n] \oplus K[n]$$

Where:

- P[n] is the  $n^{th}$  byte of the recovered plaintext.

- K[n] is the  $n^{th}$  byte of the keystream.

- C[n] is the  $n^{th}$  byte of the ciphertext.

RC4 is mathematically simple and efficient, it has several cryptographic weaknesses, such as non-random initial bytes in the keystream (susceptible to bias), and the vulnerability to key-reuse attacks (as in WEP). These weaknesses make RC4 unsuitable for modern cryptographic applications

#### 2.5.1.4. The Advanced Encryption Standard (AES)

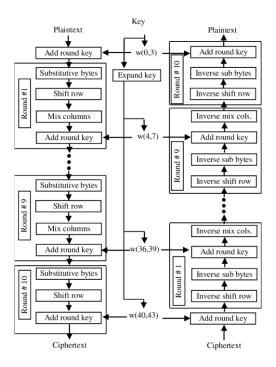

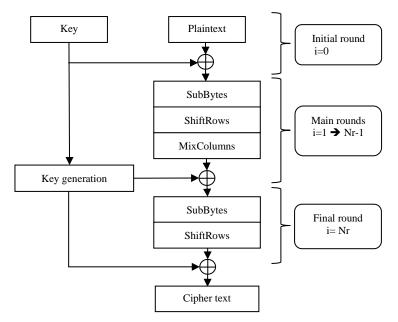

The Advanced Encryption Standard (AES) was established as the standard encryption algorithm by the National Institute of Standards and Technology (NIST) in the United States. It was officially adopted as a Federal Information Processing Standard (FIPS 197) in November 2001. AES was selected as the successor to the Data Encryption Standard (DES) after a rigorous evaluation process, which included public submissions and extensive analysis of security, performance, and efficiency [30]. AES is a symmetric block cipher that encrypts 128-bits in a single pass, and it supports 128, 192 and 256-bits key size. It was developed by Joan Daemen and Vincent Rijmen, and is commonly used algorithm especially in wireless communication. The encryption and Decryption process of AES-128 is presented in Fig. 2.10. The AES-128 means using 128-bits key length [31]. As illustrated in Fig. 2.10, the AES consists of 10 rounds in case of 128 key length, but the number of rounds is 12 and 14 in case of 192-bits and 256-bits respectively. The round in AES represents an iteration, and each iteration consists of a set of operations: AddRoundKey, SubBytes, ShiftRows, and MixColumns. These operations are performed in every round except the final round, where the MixColumns operation is omitted. The AddRoundKey operation is a XOR of the output from the previous operation and the subkey of the active round. The subkeys are generated through the key expansion process, which derives a unique subkey for each round using a series of defined operations [31].

Fig. 2.10 AES-128 Algorithm process.

The AddRoundKeyis considered the most important operation despite its simplicity, because it hides the relationship between the ciphertext and the plaintext. Here is the description of each operation in AES algorithm:

#### a- The SubBytes

The Byte substitution operation replaces each byte in the State, a 4x4 byte matrix, with a corresponding byte from the S-Box. The S-Box is a pre-calculated substitution table, where each State byte is used to index and retrieve the new byte. In this context, the S-Box provides the nonlinear substitution for each byte of the State, and is represented by the following formula:

$$S: \{0,1\}^n \to \{0,1\}^m$$

Where n is number of input bits, and m is the number of output bits.

Each byte in the AES state is treated as an element of the finite field  $GF(2^8)$ , defined by the irreducible polynomial:

$$m(x) = x^8 + x^4 + x^3 + x + 1$$

For each non-zero-byte b in  $GF(2^8)$ , the multiplicative inverse  $b^{-1}$  in the field is calculated using the following formula:

$$b. b^{-1} \mod m(x) = 1$$

Note: if b=0, its inverse is defined as 0.

The multiplicative inverse  $b^{-1}$  undergoes an affine transformation in  $GF(2^8)$  to further increase non-linearity. The transformation is defined as

$$S(b) = A.b^{-1} \oplus c$$

Where:

- $b^{-1}$  is treated as an 8-bit column vector.

- c is a constant binary vector:

$$c = [1 \quad 1 \quad 0 \quad 0 \quad 0 \quad 1 \quad 1 \quad 0]^T$$

• A is 8x8 binary matrix, defined by:

$$A = \begin{bmatrix} 1 & 0 & 0 & 0 & 1 & 1 & 1 & 1 \\ 1 & 1 & 0 & 0 & 0 & 1 & 1 & 1 \\ 1 & 1 & 1 & 0 & 0 & 0 & 1 & 1 \\ 1 & 1 & 1 & 1 & 0 & 0 & 0 & 1 \\ 1 & 1 & 1 & 1 & 1 & 0 & 0 & 0 \\ 0 & 1 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 1 & 1 & 1 & 1 & 1 & 1 \end{bmatrix}$$

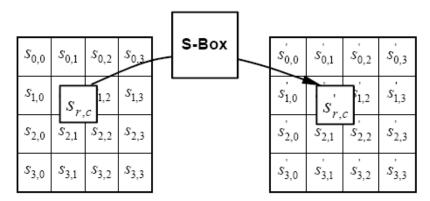

The SubBytes operation is illustrated in Fig. 2.11. the SubBytes operation relays on the s-box table to replace bytes.

Fig. 2.11 SubBytes operation in AES algorithm.

#### b- ShiftRows

ShiftRows is permutation step that operates on the state matrix to introduce diffusion to the AES algorithm. It consists on re-arranging the bytes in each row of the state by shifting them to the left [32]. The state matrix is defined as follows:

$$S = \begin{bmatrix} S_{0,0} & S_{0,1} & S_{0,2} & S_{0,3} \\ S_{1,0} & S_{1,1} & S_{1,2} & S_{1,3} \\ S_{2,0} & S_{2,1} & S_{2,2} & S_{2,3} \\ S_{3,0} & S_{3,1} & S_{3,2} & S_{3,3} \end{bmatrix}$$

Where each element  $s_{i,j}$  represents a byte.

The first row remains unchanged, the second row is shifted left by 1 byte, the third row and the fourth row are shifted by 2 and 3 bytes respectively, the mathematical description of this operation is defined as follows:

$$S_{i,j} \rightarrow S_{i,(j-i) \mod 4}$$

According to this definition, the state presented gives the following state after applying the ShiftRows operation:

$$S' = \begin{bmatrix} s_{0,0} & s_{0,1} & s_{0,2} & s_{0,3} \\ s_{1,1} & s_{1,2} & s_{1,3} & s_{1,0} \\ s_{2,2} & s_{2,3} & s_{2,0} & s_{2,1} \\ s_{3,3} & s_{3,0} & s_{3,1} & s_{3,2} \end{bmatrix}$$

The ShiftRows operation ensures that the bytes in each column depend on bytes from multiple rows after the subsequent MixColumns step that will be described in the following section. It also prevents having independent columns during the encryption which render security weak.

#### c- MixColumns

This operation is a linear transformation of data applied to the state columns. It mixes the bytes of each column of the state matrix to provide diffusion across the ciphertext which ensures that changes in each bytes affects other bytes [32]. Each column is multiplied by a fixed 4x4 matrix in  $GF(2^8)$  as follows:

$$\begin{bmatrix} s'_{0,c} \\ s'_{1,c} \\ s'_{2,c} \\ s'_{3,c} \end{bmatrix} = \begin{bmatrix} 2 & 3 & 1 & 1 \\ 1 & 2 & 3 & 1 \\ 1 & 1 & 2 & 3 \\ 3 & 1 & 1 & 2 \end{bmatrix} \cdot \begin{bmatrix} s_{0,c} \\ s_{1,c} \\ s_{2,c} \\ s_{3,c} \end{bmatrix}$$

Where:

- The coefficients 1,2 and 3 are constants in  $GF(2^8)$

- The multiplication is performed modulo  $x^8 + x^4 + x^3 + x + 1$

The multiplication and addition performed in  $GF(2^8)$  using XOR for addition and finitr field multiplication for products. The output bytes are:

$$s'_{0,c} = (2. \ s_{0,c}) \oplus (3. s_{1,c}) \oplus (1. s_{2,c}) \oplus (1. s_{3,c})$$

$$s'_{1,c} = (1. \ s_{0,c}) \oplus (2. s_{1,c}) \oplus (3. s_{2,c}) \oplus (1. s_{3,c})$$

$$s'_{2,c} = (1. \ s_{0,c}) \oplus (1. s_{1,c}) \oplus (2. s_{2,c}) \oplus (3. s_{3,c})$$

$$s'_{3,c} = (3. \ s_{0,c}) \oplus (1. s_{1,c}) \oplus (1. s_{2,c}) \oplus (2. s_{3,c})$$

Multiplication in  $GF(2^8)$ :

1.

$$x = x$$

2.  $x = left shift (x \ll 1), reduced modulo (x^8 + x^4 + x^3 + x + 1)$

3.  $x = (2.x) \oplus x$

The transformation matrix for decryption is:

$$\begin{bmatrix} 14 & 11 & 13 & 9 \\ 9 & 14 & 11 & 13 \\ 13 & 9 & 14 & 11 \\ 11 & 13 & 19 & 14 \end{bmatrix}$$

The MixColumns operation is presented in Fig. 2.12.

Fig. 2.12 MixColumns operation.

#### d- AddRoundKey

At this step the encryption process meets the Key generation process. The State in AddRoundKey is XORed with the round Subkey [32]. This operation is defined mathematically as follows:

$$s'_{i,i} = s_{i,i} \oplus k_{i,i}$$

Where:

- $s_{i,j}$ : Byte in the state matrix.

- $k_{i,j}$ : Corresponding byte in the round key matrix.

- $s'_{i,j}$ : Resultant byte in the transformed state matrix.

The inputs to the AddRoundKey is:

The state

$$S = \begin{bmatrix} s_{0,0} & s_{0,1} & s_{0,2} & s_{0,3} \\ s_{1,0} & s_{1,1} & s_{1,2} & s_{1,3} \\ s_{2,0} & s_{2,1} & s_{2,2} & s_{2,3} \\ s_{3,0} & s_{3,1} & s_{3,2} & s_{3,3} \end{bmatrix}$$

The Key

$$k = \begin{bmatrix} k_{0,0} & k_{0,1} & k_{0,2} & k_{0,3} \\ k_{1,0} & k_{1,1} & k_{1,2} & k_{1,3} \\ k_{2,0} & k_{2,1} & k_{2,2} & k_{2,3} \\ k_{3,0} & k_{3,1} & k_{3,2} & k_{3,3} \end{bmatrix}$$

The output of the AddRoundKey is:

The output

$$S' = \begin{bmatrix} s_{0,0} \oplus k_{0,0} & s_{0,1} \oplus k_{0,1} & s_{0,2} \oplus k_{0,2} & s_{0,3} \oplus k_{0,3} \\ s_{1,0} \oplus k_{1,0} & s_{1,1} \oplus k_{1,1} & s_{1,2} \oplus k_{1,2} & s_{1,3} \oplus k_{1,3} \\ s_{2,0} \oplus k_{2,0} & s_{2,1} \oplus k_{2,1} & s_{2,2} \oplus k_{2,2} & s_{2,3} \oplus k_{2,3} \\ s_{3,0} \oplus k_{3,0} & s_{3,1} \oplus k_{3,1} & s_{3,2} \oplus k_{3,2} & s_{3,3} \oplus k_{3,3} \end{bmatrix}$$

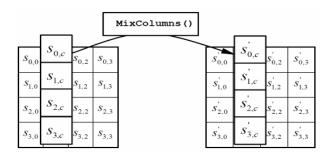

#### e- Key Generation

The key generation is the process of generating subkeys for each round starting from the initial key. Number of rounds as mentioned before is 10, 12 or 14 depending on the length of the key, 128, 192 or 256 respectively. The initial key is divided into 4-byte words (W[i]). Number of words  $N_K$  is 16,

24 or 32 according the key length 128, 192 or 256. The process of key generation is presented in Fig. 2.13.

Figure 5.9 AES Key Expansion

Fig. 2.13 Key generation process in AES algorithm.

The total number of words in the expended key is:

$$N_h x (N_r + 1)$$

Where:

- $N_b = 4$ : Number of columns in the state matrix

- $N_r$ : Number of rounds (10, 12 or 14)

The round constant (RCON) is a table of constants used in the key expansion to add a nonlinearity to the output. RCON[i] is divided from power of 2 in the finite field  $GF(2^8)$ :

$$RCON[1] = 0x01, RCON[2] = 0x02, RCON[3] = 0x04, ...$$

The steps to expend the key are:

For

$$i < N_k$$

:

The initial key word W[0] to  $W[N_k - 1]$  are directly copied from the original key

For

$$i \ge N_k$$

:

$$W[i] = W[i - N_k] \oplus T(W[i - 1])$$

If  $i \bmod N_k = 0$  Or  $W[i] = W[i - N_k] \oplus W[i - 1]$

T function (For  $i \bmod N_k = 0$ ):

Rotate W[i-1]: Circularly rotate the bytes by one position.

Substitute bytes from the S-box as described in the SubByte section.

XOR the first byte of the word with  $RCON[i/N_K]$ .

The following step is additional for the 256-bits key length:

If  $i \mod N_k = 4$ , the [i-1] word is substituted using S-box table.

# 2.5.2. Message authentication codes (MAC)

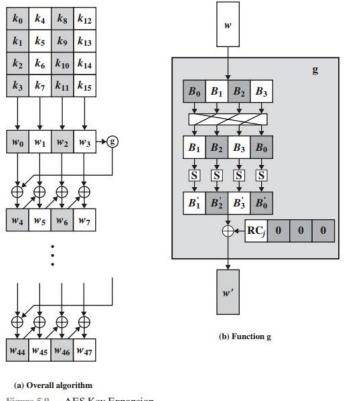

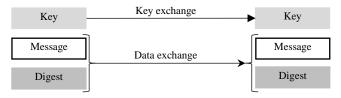

Message authentication codes is the concept of combining a message with a secret key before hashing. The purpose is to detect alterations of the message or the digest. While this may appear similar to the definition and purpose of hashing outlined in the preceding sections, it is, in fact, distinct. Hashing alone is not enough when sending packets across a communication channel, the reason is that the digest (result of hashing) is sent alongside the original message to enable the receiver to verify if the message has been altered or damaged. However, in a scenario where the message is intercepted and modified, with calculation of the new digest, the receiver would generate the same altered digest. As a result, the receiver would remain unaware that the message has been tampered. To address this issue, and given that the hash function ensures data integrity rather than message confidentiality, the Message authentication codes is the optimal solution for this issue, the process of MAC is illustrated in the Fig. 2.14.

Fig. 2.14 Message Authentication Code.

An important characteristic on hashing is that the order is important, which means combining Message + Key is different that combining Key + Message. So, even if the key is the same, and the message is the same but the order is different, the receiver will not get the same digest, that's where a Hash-Based Message Authentication Code (HMAC) comes into play. HMAC is merely a standard way of combining a message and a key so if transmitter and receiver want to speak in a way that guarantees the integrity of the message, they not only have to agree upon using the concept of combining a message and a key, but they also have to agree on combining that message and a key in a specific way. HMAC is defined and detailed in RFC 2104 [33]. it includes all the instructions for exactly how you can combine a message and a key, in order to guarantee integrity of that message.

Table 2.3 lists some standard way of combining a message and a secret key to guarantee message integrity.

Table 2.3. Commonly used standards for message integrity

| Legacy | -                      |

|--------|------------------------|

| Modern | HMAC, Poly1305         |

| Future | GCM, CCM, AEAD Ciphers |

# 2.5.3. Pseudo Random Functions (PRF)

Pseudo random function is similar as hashing function, except for output which is arbitrary length, meaning that the length is controllable. It's like a hashing algorithm that feeds back in on itself. The purpose of a PRF is to use a single key to generate an unlimited number of keys. In secure communication, a PRF enables the transmitter and receiver to derive multiple secret keys from a shared secret key, which can then be used for data encryption (confidentiality) and MAC (authentication and integrity). This approach eliminates the need for multiple key exchanges, which is a complex and risky operation. The diagram in Fig. 2.15 represent the PRF function.

Fig. 2.15 Pseudo Random Function diagram.

If a PRF is running using only the key and data length input, the same output will be generated each time, because the starting information (seed data) hasn't changed, the seed data allows to differentiate the pseudo random data [34]. The PRF function is defined as follows:

$$F: \{0,1\}^k \times \{0,1\}^n \to \{0,1\}^m$$

Input Key  $k \in \{0,1\}$  (secret and fixed)

Seed data  $x \in \{0,1\}$

Output Pseudo random  $m \in \{0,1\}$

#### 2.5.4. Key Derivation Function (KDF)

KDF is similar to a PRF but requires also an additional random data that is mixed into the initial data, and a Slowdown mechanism. The purpose of this extra data, which is known also by the name "Salt" is to guarantee a minimum level of entropy, while the Slowdown mechanism can be any one of a number of strategies, like running the KDF for a certain number of iterations instead of going straight from input to Output by recalculating the output several times through the same KDF, or through using a memory intensive match, or even prevent parallelization intestinally.

The purpose of a KDF is to make brute forcing the output infeasible. A good example of this is password storage, it is commonly known that it's better to use longer passwords, but there's probably a lot of people that are still using eight-character passwords or even less, that's where salt comes into play, salt adds some level of randomness to the password so that even in case of an insecure five-character password, salt might add another 40 characters to it, making it more secure. Additionally, passwords to online application are not stored in clear text on servers because it is insecure, but instead they are stored on a sort of hash of that password combined with the salt to enhance security. Furthermore, hashing and PRF are built for Speed, whereas KDFs are intentionally built to slow down the process, that's because modern cracking array can run through calculations of hashes on PRFs at a rate of billions or even trillions per second, but if each of those calculations is slightly slow down, it takes years to do the same number of guesses [36]. The KDF function is described as follows:

$$KDF(S, P) \rightarrow k$$

Where:

- S is the secrete input (e.g., a password)

- *P* is optional contextual information (e.g., salt)

- K is the derived key(s) of the desired length

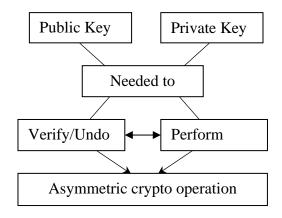

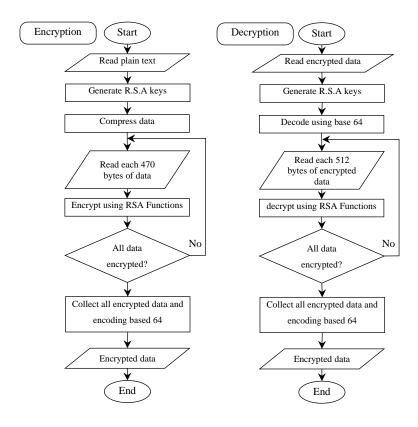

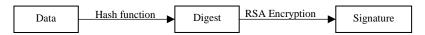

## 2.6. Asymmetric cryptography