#### THE PEOPLE'S DEMOCRATIC REPUBLIC OF ALGERIA

#### MINISTRY OF HIGHER EDUCATION AND SCIENTIFIC RESEARCH

#### **UNIVERSITY OF FERHAT ABBAS SETIF-1(ALGERIA)**

#### FACULTY OF TECHNOLOGY

Field: Science and Technology

## **THESIS**

**Presented to the Department of Electronics**

For the graduation of

## DOCTORATE

**Option: Electronics of Embedded System and Technology**

By

## **ABDENOUR ALLALI**

## **THEME**

## Contribution to the FPGA implementation of an embedded system for ECG signals

Defended on 19/11/2022 (1444 / ربيع الثاني / 25) before the jury composed of:

| AMARDJIA Noureddine    | Professor | Univ. Sétif 1 | Electronique | President  |

|------------------------|-----------|---------------|--------------|------------|

| ZIET Lahcene           | Professor | Univ. Sétif 1 | Electronique | Supervisor |

| CHEMALI Hamimi         | Professor | Univ. Sétif 1 | Electronique | Examiner   |

| FERHAT Hemida Abdelhak | Professor | Univ. Sétif 1 | Electronique | Examiner   |

| BEKKOUCHE Tewfik       | MCA       | Univ. BBA     | Electronique | Examiner   |

| BENSOUAG Abdennour     | MAA       | CHU. Sétif 1  | Médecine     | Guest      |

| BARTIL Arres           | Professor | Univ. Sétif 1 | Electronique | Guest      |

يسم الله الترخمن التّحيير ٱلْحَمْلُ بِتْلُورَتِ الْعْلَمِينَ الْتَحْمَنِ الرَّحْمَنِ الرَّحِيْمِ الْ مْلِكِ يَوْمِ الدِّيْنِ ﴿ إِيَاكَ نَعُبُدُ وَإِيَّاكَ نَسْتَعِيْنُ إِهْدِ نَاالِصَرَاطَ الْمُسْتَقِيْحَ فِحَرَاطَ الَّذِينَ ٱنْعَمْتَ عَلَيْهِمْ خَيْرِالْمُغْضُوْبِعَلَيْهُمُ وَلَالصَّالَيْنَ ٥

## Praise be to Allah alone, He has no partner My Prayers on Muhammad, the Prophet of Allah

To my dear parents and my wife's parents To my dear wife and daughter (Ilef) To my family

#### ACKNOWLEDGEMENT

I would like to thank Mr Lahssen Ziat and Arres Bartil, professors at the University of Farhat Abbas Setif-1, for agreeing to be Supervisors of my thesis.

I would like also to express my sincere gratitude to each of Mr Abdelouahab Hassam, Hamimi Chemmali and Saad Bouguezal, the professors at the University of Farhat Abbas Setif-1, for their useful comments and instructions during the period of study and scientific research.

I would like to thank Mr Noureddine Amardjia Professor at the University of Farhat Abbas Setif -1, for his acceptance of chairing the jury.

I thank Mr Tewfik Bekkouche, Senior Lecturer at the University of BBA, To agree to be a member of the jury.

I thank Mr Ferhat Hemida, Professor at the University of Farhat Abbas Sétif 1, for his acceptance, to be a member of the jury.

Warmly, I would like to thank Mr Abdennour Bensouag, Senior Lecturer at the Faculty Medicine in the University of Farhat Abbas Setif-1, Doctor at CHU Abdennour Saadna, that welcoming me to his laboratory more than one time and providing me with the necessary information on cardiac physiology and the means available to do this work.

In the same way, I would like to thank Ms Biljana Stosic, Professor at the Faculty of Electronic Engineering at the University of Nice, Serbia, a senior member of IEEE and a member of the National Society of Microwave Technology in Serbia, for all her observations and useful statements during the investigation of my first article.

I give my thanks and gratitude to Mr Farid Amirouche, Professor and Director of Orthopaedic and Biomechanics research at the University of Illinois at Chicago and Northshore University Health Systems, Evanston, IL. Who in turn gave me his precious time to review and study this thesis, especially in terms of language.

I thank all, for accepting to study this work.

## Acronyms

ADC/DAC Analog to Digital Convert/Digital to Analog Convert

AFDW Alexander Fractional Differential Window

AICF Adaptive Impulse Correlated Filter

ANN Artificial Neural Networks

ANOVA ANalysis Of VAriance

AP Action Potential

AP All Programmable

ARF Adaptive Recurrent Filter

ARP Absolute Refractory Period

ASIP Application-Specific Instruction Processors

ASSP Application Specific Standard Product

ASSP Application-Specific System Processor

AV Atrio-ventricular node

BC Best Configuration

**BLW** Baseline Wander

**BSF** Band Stop Filter

**BSPM** Body Surface Potential Mapping

**CISC** Complex Instruction Set Computer

CVD Cardiovascular Diseases

**DAD** Delayed After Depolarization

**DMA** Direct Memory Access

**DSP** Digital Signal Processing

DWT Discrete Wavelet Transform

**DWT** Discrete Wavelet Transforms

EAD Early After Depolarization

ECG Electrocardiogram

EDK Embedded Design Kit

**EMD** Empirical Mode Decomposition

EMG Electromyography

FDA Filter Design and Analysis

FFT Fast Fourier Transform

FIR Finite Impulse Response

**FPGA** Field Programmable Gate Array

GPIO General Purpose Input/Output

HPF High Pass Filter

HRT Heart Rate Turbulence

HRV Heart Rate Variability

ICA Independent Component Analysis

**IDWT** Inverse Discrete Wavelet Transform

**IIR** Infinite Impulse Response

**INA** Instrumentation Amplifier

**ISCS** Intra-ventricular Special Conduction System

**ISE** Integrated Software Environment

LMS Least Mean Square

LPF Low Pass Filter

LUT Lookup Tables

MADALINE Multiple ADAptive LINear Element

MSE Mean Square Error

NLMS Normalized Least Mean Square

**NRF** Noise Reduction Factors

PCA Principal Component Analysis

PLI Power Line Interference

**PNR** Percentage Noise Retention Ratio

**PS** Processing System PTB Physikalisch-Technische Bundesanstalt **RISC** Reduced Instruction Set Computer **RRP** Relative Refractory Period **RTOS** Real-Time Operating System SA Sino-atrial node SCD Sudden Cardiac Death **SCI** Serial Communication Interfaces SCS Special Conduction System SDLMS Sign Data Least Mean Square SELMS Sign Error Least Mean Square SNR Signal to Noise Ratio SoC System on Chip SoPC System on Programmable Chip SSLMS Sign-Sign Least Mean Square **STFT** Short-Time Fourier Transform **SVM** Support Vector Machine **TRP** Total Refractory Period TSAF Time-Sequenced Adaptive Filter **USB** Universal Serial Bus VCG Vector cardiogram **VHDL** VHSIC Hardware Description Language **VLSI** Very Large Scale Integration **WGN** White Gaussian Noise WT Wavelet Transforms **XSG** Xilinx System Generator

## Contents

| Abstract                                           | 1         |

|----------------------------------------------------|-----------|

| Introduction.                                      | 2         |

| Chapter I: Anatomy and functionality of the hu     | man heart |

| 1.1 Introduction         1.2 Cardiovascular system |           |

| 1.2.1 Arterial and venous circulation              | 9         |

| 1.2.2 The heart of the human body                  | 9         |

| 1.2.3 Cardiovascular physiology                    | 10        |

| 1.3 Functioning of the heart                       | 10        |

| 1.3.1 The Cardiac mechanical activity              |           |

| 1.3.2 Electrical activation of the heart           | 11        |

| 1.3.2.1 Potential for rest and action              | 11        |

| 1.3.2.2 Automation                                 | 14        |

| 1.3.2.3 Heart Conduction                           | 14        |

| 1.3.2.4 Excitation and contraction coupling        |           |

| 1.3.2.5 Coronary circulation                       |           |

| 1.3.2.6 Coronary blood flow                        |           |

| 1.3.2.7 Myocardial metabolism                      | 16        |

| 1.3.2.8 Myocardial ischemia and necrosis           | 16        |

| 1.4 Cardiac cycle                                  | 17        |

| 1.4.1 Ventricular systole                          | 17        |

| 1.5 Electrocardiogram ECG                          |           |

| 1.5.1 ECG Waves and Intervals                      |           |

| 1.5.2 Derivatives                                  |           |

| 1.5.2.2 Three unipolar leads                       |           |

| 1.6 ECG Monitoring Devices                         |           |

| 1.6.1 Traditional ECG Monitoring                   |           |

| 1.6.2 Real-Time ECG Monitoring                     |           |

| 1.6.2.1 HOLTER monitoring                          |           |

| 1.7 PTB Diagnostic ECG Database                    |           |

| 1.8 ECG signal problems during the Acquisition     |           |

| 1.8.1 Reversals lead  | 30 |

|-----------------------|----|

| 1.8.2 Artifacts       | 30 |

| 1.8.3 Filter settings | 30 |

| 1.9 Conclusion        | 31 |

| ferences |

|----------|

|----------|

## Chapter II: A Review on Biomedical ECG signal Filtering and Analysis

| 2.1 Introduction.                           |    |

|---------------------------------------------|----|

| 2.2 ECG Characteristics                     | 36 |

| 2.2.1 ECG signal acquisition                |    |

| 2.2.2 Non-stationarity of ECG signal        |    |

| 2.3.2 ECG Signal and Artifacts              |    |

| 2.2.3.1 Baseline Wander (BLW)               |    |

| 2.2.3.2 Power Line interference (PLI)       | 40 |

| 2.2.3.3 Electromyography (EMG) noise        | 41 |

| 2.2.4 Other artifacts.                      |    |

| 2.2.4.1 Motion Artifacts                    | 42 |

| 2.2.4.2 Electrode pop or contact noise      | 43 |

| 2.2.4.3 Electrosurgical noise               | 43 |

| 2.2.4.4 Amplifier noise                     | 43 |

| 2.2.4.5 Quantization noise                  | 44 |

| 2.5 Motivation of filtering                 | 44 |

| 2.6 De-noising Techniques                   | 46 |

| 2.6.1 Wavelet Transform                     | 50 |

| 2.6.1.1 Decomposition of the singular value | 52 |

| 2.6.2 Adaptive filtering                    | 52 |

| 2.6.2.1 Diagram                             | 54 |

| 2.6.2.2 Adaptive Algorithms                 |    |

| 2.7 Digital filtering                       |    |

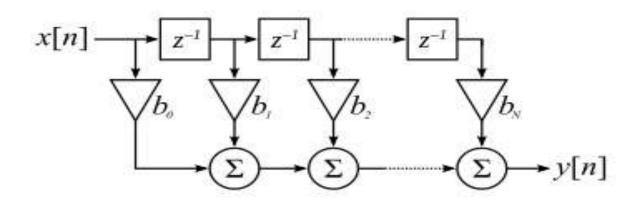

| 2.7.1 FIR and IIR filtering                 | 57 |

| 2.7.1.1 Structure of the IIR filter       | 58 |

|-------------------------------------------|----|

| 2.7.2 FIR Filters Design Techniques       | 58 |

| 2.7.2.1 FIR Filter Design Based on Window | 59 |

| 2.8 Conclusion                            | 63 |

| References | 55 |

|------------|----|

|------------|----|

## Chapter III: SoC platforms based on programmable circuits

| 3.1 Introduction                        | 69 |

|-----------------------------------------|----|

| 3.2 ASIC design                         | 70 |

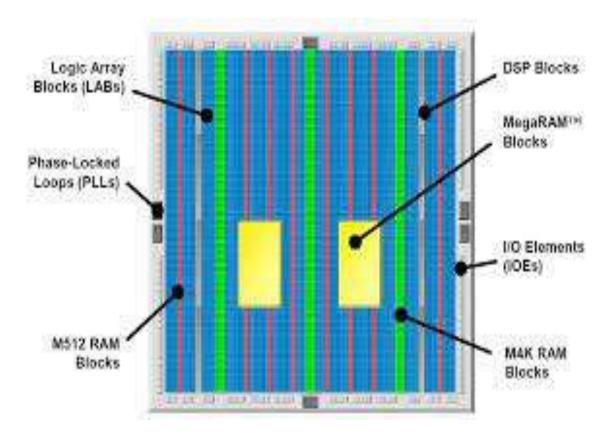

| 3.3 FPGA design                         | 71 |

| 3.3.1 Main manufacturers for FPGA       | 71 |

| 3.3.2 Different Types of FPGA Circuits  | 72 |

| 3.3.3 Xilinx FPGA Technology            | 73 |

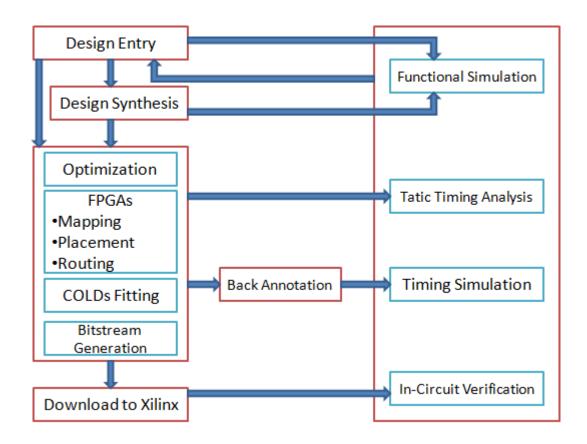

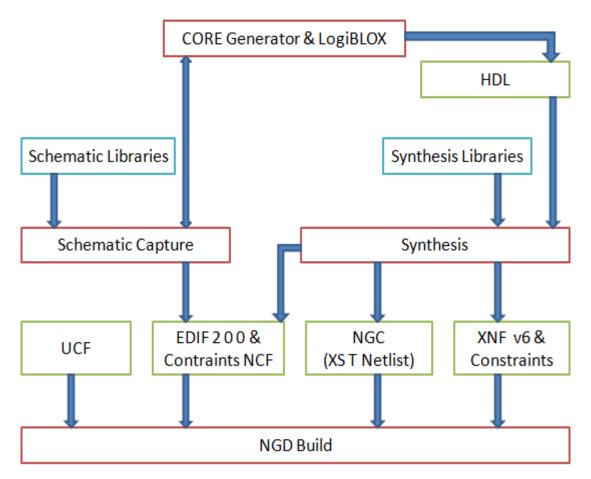

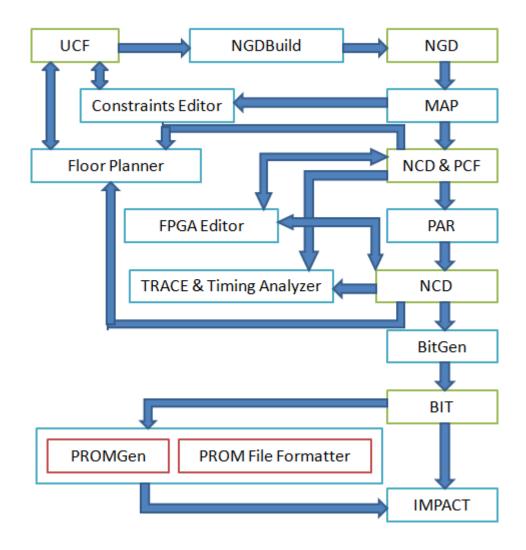

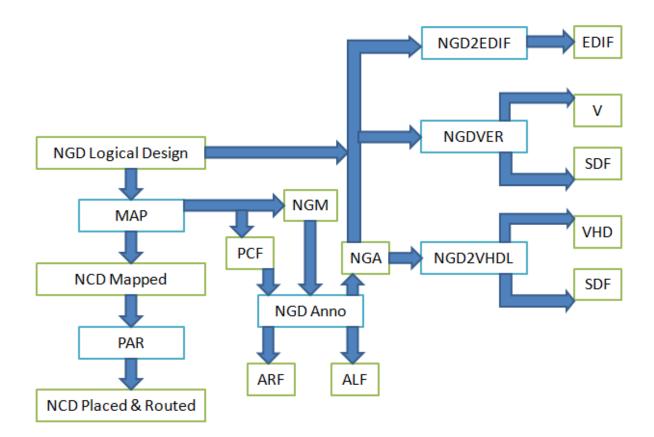

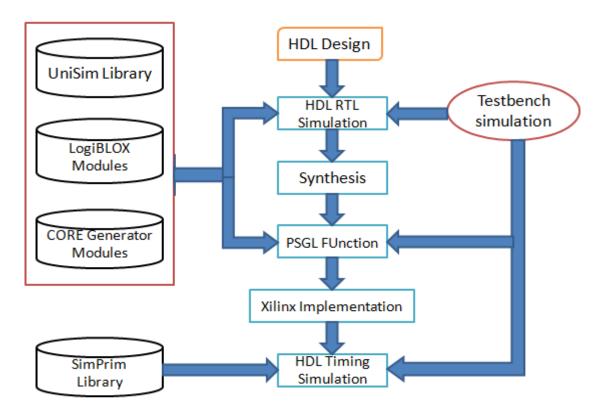

| 2.3.5 FPGA design flow                  | 76 |

| 3.4 Xilinx Zynq overview                | 77 |

| 3.4.1 Zynq Design Flow                  |    |

| 3.4.2 Application Processing Unit (APU) | 79 |

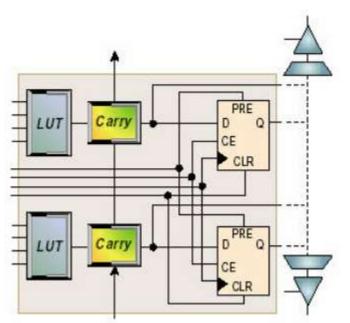

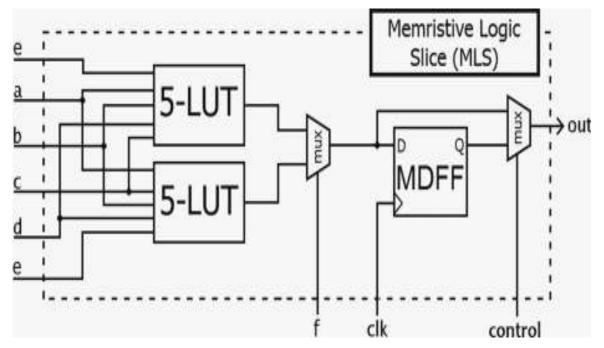

| 3.4.3 Programmable Logic Structure      | 81 |

| 3.5 Design and Synthesis                |    |

| 3.6 Hierarchical Design                 |    |

| 3.6.1 Schematics                        | 83 |

| 3.6.2 Elements of Libraries             |    |

| 3.7 Core Generation Tool                |    |

| 3.8 HDL and synthesis                   |    |

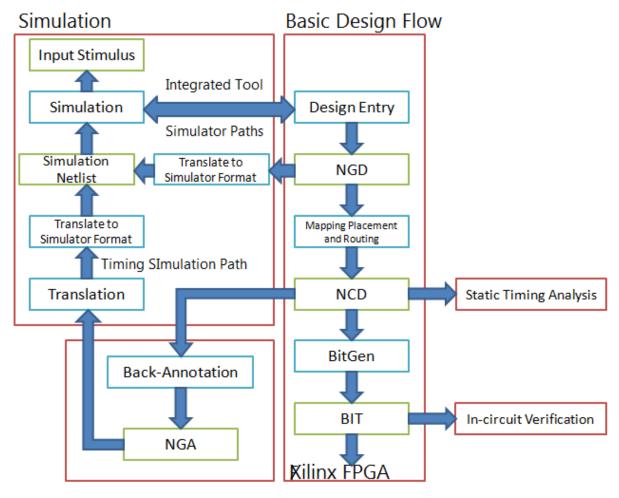

| 3.9 Functional simulation               |    |

| 3.10 Constraints                        |    |

| 3.10.1 Mapping Constraints              |    |

| 3.10.2 Placement Constraints            |    |

| 3.10.3 Time constraints                 |    |

| 3.10.4 Translation to Net List          |    |

| 3.10.5 Implementation                   |    |

| 3.10.6 Mapping                                  | 86 |

|-------------------------------------------------|----|

| 3.10.7 Placement and Routing                    | 87 |

| 3.10.8 Bitstream generation                     | 87 |

| 3.10.9 Verification                             | 87 |

| 3.10.10 Schematic based Simulation              | 90 |

| 3.10.11 Functional Simulation                   | 90 |

| 3.10.12 Temporal Simulation                     | 90 |

| 3.10.12 HDL based Simulation                    | 91 |

| 3.10.13 Static Time Analysis                    | 91 |

| 3.10.14 Circuit Check                           | 92 |

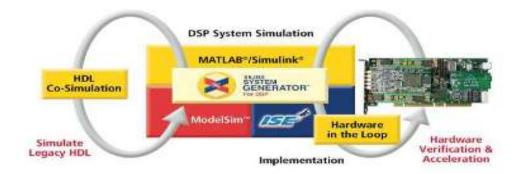

| 3.11 Xilinx System Generator                    | 92 |

| 3.12 VHSIC Hardware Description Language (VHDL) | 93 |

| 2.13Conclusion                                  | 94 |

| References                                      | 95 |

## Chapter IV: ECG de-noising and FPGA implementation

| 4.1 Introduction                                                           | 97  |

|----------------------------------------------------------------------------|-----|

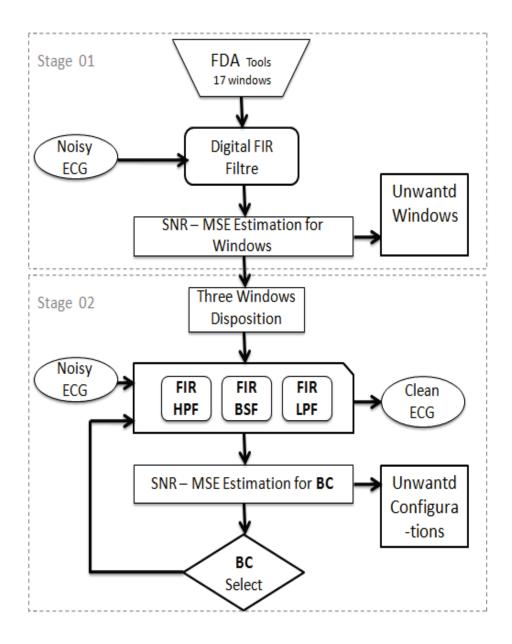

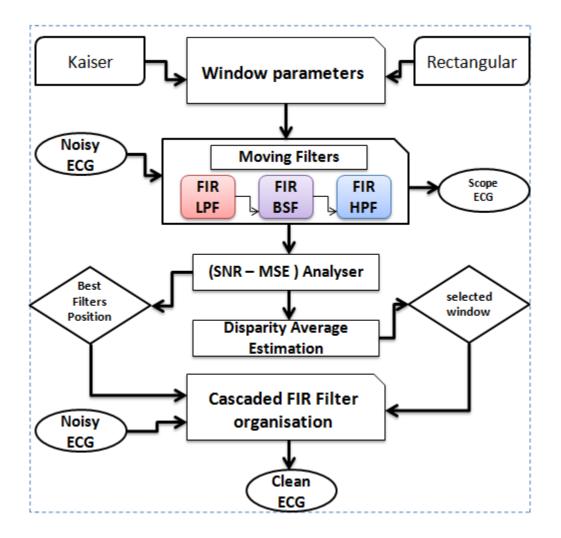

| 4.2 Methodology of ECG signal Denoising using FIR Filter                   |     |

| 4.2.1 Digital FIR Filter                                                   | 100 |

| 4.2.2 Cascaded Filter Technology                                           | 101 |

| 4.2.3. FDA Tools and Window Function                                       | 101 |

| 4.2.4 ECG Database Overview                                                |     |

| 4.2.5 White Gaussian Noise (WGN) and EMG Approximation                     | 102 |

| 4.2.6 SNR and MSE Parameters                                               | 102 |

| 4.3 ECG Preprocessing and Filtering Methods                                | 103 |

| 4.3.1 ECG De-noising based on the Selection of Cascaded FIR Filter Windows | 103 |

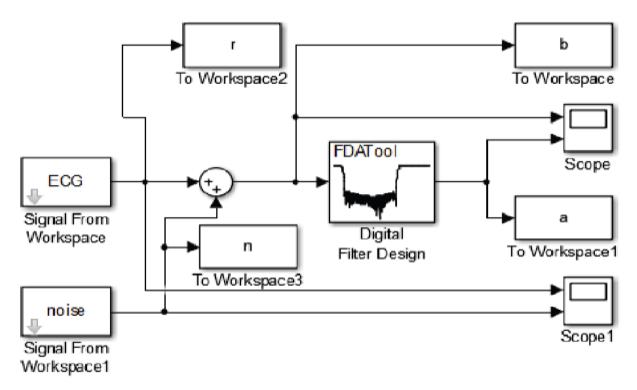

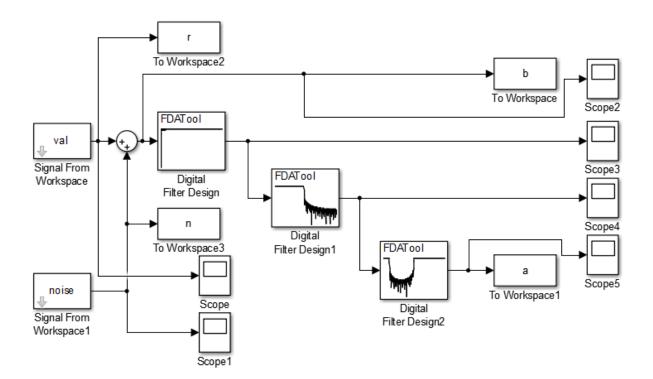

| 4.3.1.1 Matlab Simulink Imptementation                                     | 106 |

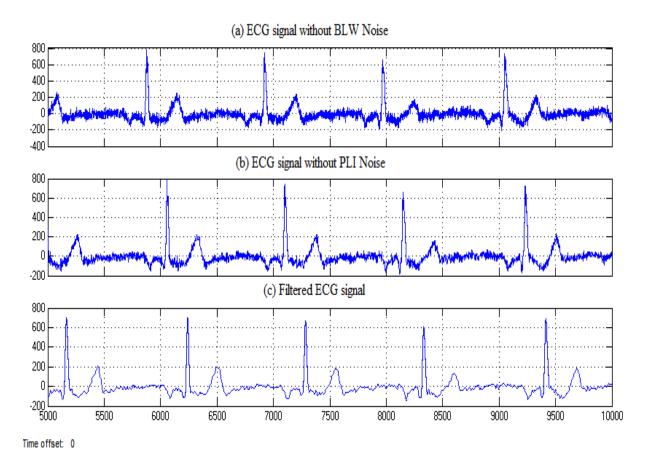

| 4.3.1.2 Results evaluation and discussion                                  | 107 |

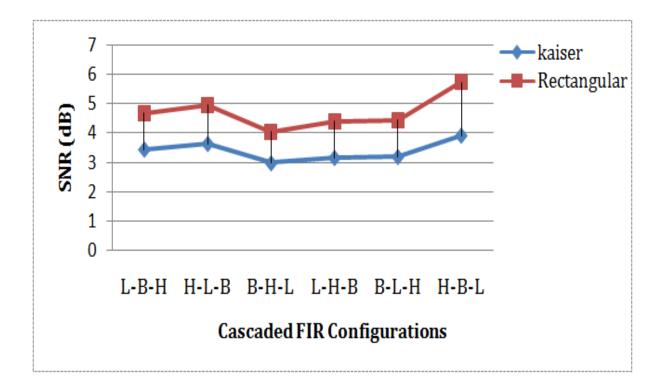

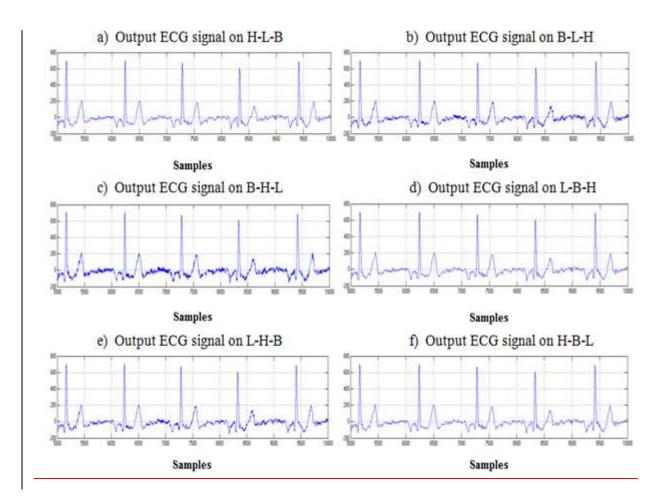

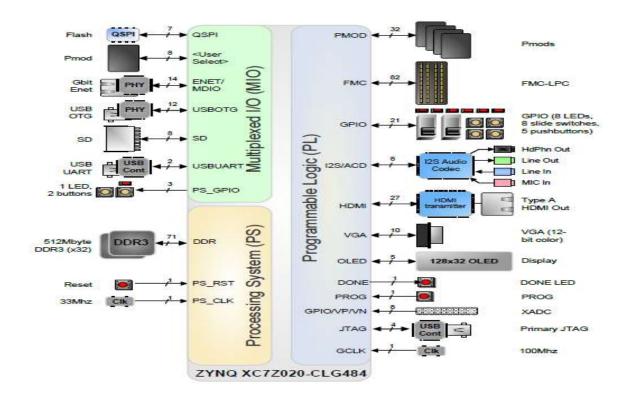

| 4.3.2 Evaluating the Influence of filters position in the cascaded filter  | 112 |

| 4.3.2.1 ECG De-noising performance based on filters positions              | 114 |

| 4.3.2.2 Results evaluation and discussion                                  | 116 |

| 4.3.2.3 The ANOVA results                                                  | 117 |

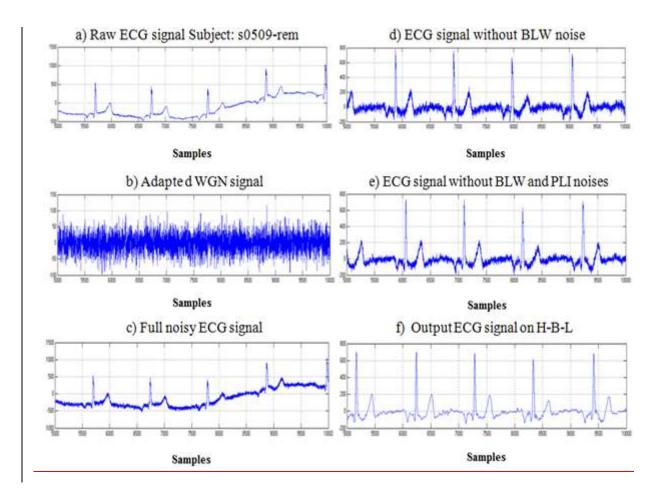

| 4.3.2.4 ECG De-noising based on H-B-L configuration                        | 117 |

| 4.3.2.5   | ECG       | De-noising     | based    | the    | comparison    | the     | morphologies | of       | deferent |

|-----------|-----------|----------------|----------|--------|---------------|---------|--------------|----------|----------|

| configura | ations    |                |          |        |               |         |              | •••••    | 119      |

| 4.4 Conf  | irmatio   | n on other EC  | Gs diag  | nostic | class         |         |              |          |          |

| 4.5 Com   | parison   | of the propos  | ed appro | oaches | with existing | works   | 5            | •••••    | 122      |

| 4.6 Resu  | lts and   | Discussion     |          |        |               |         |              |          | 122      |

| 4.7 Exter | nsions t  | o the Embedd   | ed Syste | em usi | ng FPGA imp   | lemen   | tation       | •••••    |          |

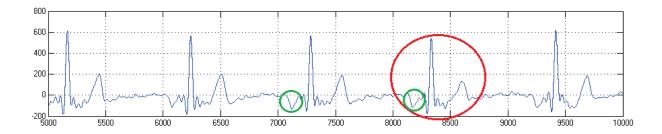

| 4.7.1 Int | roductio  | on to the XILI | NX Zed   | Board  |               | •••••   |              |          |          |

| 4.7.2 Pro | gramm     | able SoC       |          | •••••  |               |         |              | •••••    |          |

| 4.7.3 Ins | tallation | n and Usage    |          | •••••  |               | •••••   |              |          | 126      |

| 4.7.4 Ha  | rdware    | ZedBoard Set   |          | •••••  |               | •••••   |              | •••••••• | 127      |

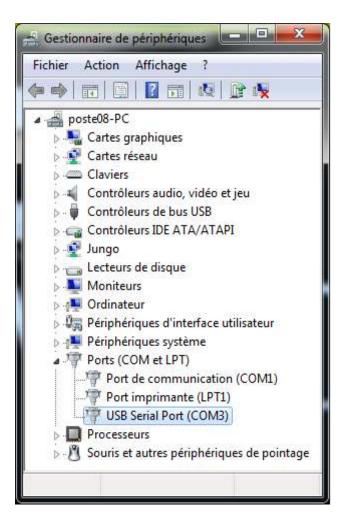

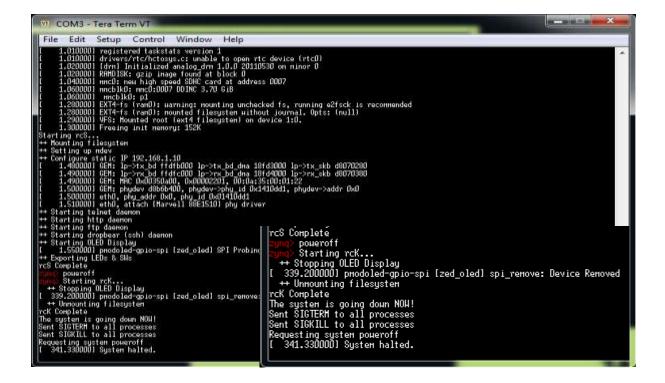

| 4.7.5 Lin | ux Star   | tup and Shutc  | lown     | •••••  |               | •••••   |              | •••••    | 131      |

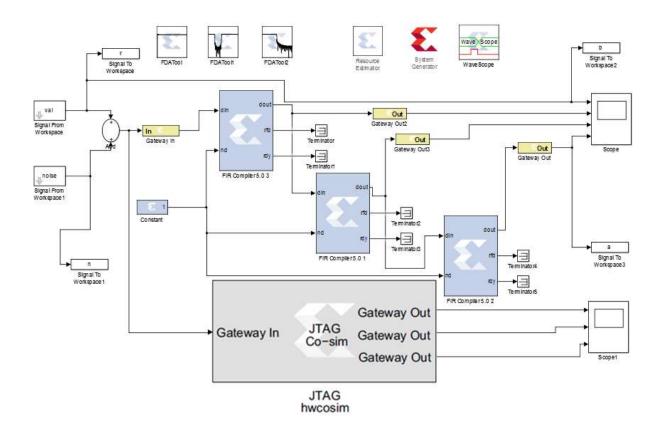

| 4.8 FPG.  | A imple   | ementation wi  | th MAT   | LAB S  | System Genera | ator co | nfiguration  | •••••    | 132      |

| 4.8.1 Ha  | rdware    | Co-Simulatio   | n Featur | es     |               | •••••   |              |          | 134      |

| 4.9 Conc  | lusion    | and Future dir | ection w | ork    |               | •••••   |              |          | 135      |

| Referenc  | es        |                |          |        |               |         |              | •••••    | 137      |

| Conclu    | ision.    |                | •••••    |        |               |         |              |          | 140      |

## **List of Figures**

## Chapter I: Anatomy and functionality of the human heart

| Figure 1.1 movements of the walls and valves (arrows)               | 8  |

|---------------------------------------------------------------------|----|

| Figure 1.2 Wiggers diagram of the cardiac cycle                     | 11 |

| Figure 1.3 Potentials of the nodal tissue                           | 12 |

| Figure 1.4 the action potential in the cells                        | 13 |

| Figure 1.5 electrical conduction system of the heart                | 15 |

| Figure 1.6 different times and evolution of intracavitary pressures | 17 |

| Figure 1.7 electrical system in the heart                           | 19 |

| Figure 1.8 an electrocardiogram ECG wave                            |    |

| Figure 1.9 Electrocardiogram ECG trace                              | 21 |

| Figure 1.10 The derivations of Einthoven                            | 23 |

| Figure 1.11 Unipolar precordial leads                               | 24 |

| Figure 1.12 Holter monitoring test                                  |    |

# Chapter II: A Review on Biomedical ECG signal Filtering and Analysis

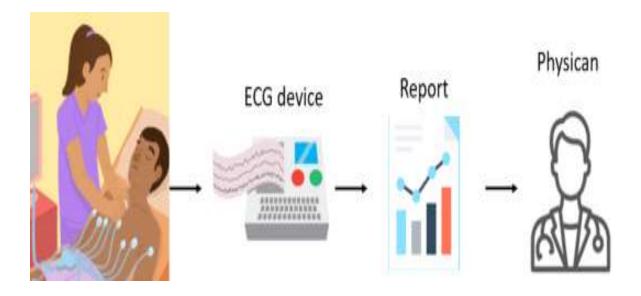

| Figure 2.1 Acquisition of the electrical activity of the human heart                        | 37 |

|---------------------------------------------------------------------------------------------|----|

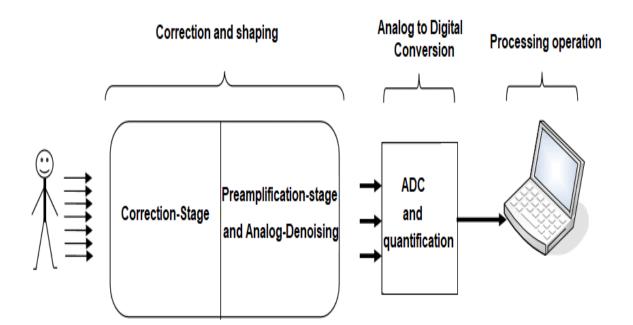

| Figure 2.2 The acquisition chain                                                            | 38 |

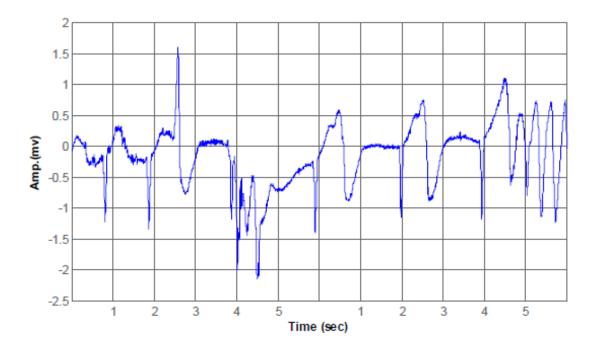

| Figure 2.3 shows ECG interval with arrhythmias Changes in the morphology and heart ra       | te |

| have a non-stationary nature                                                                | 39 |

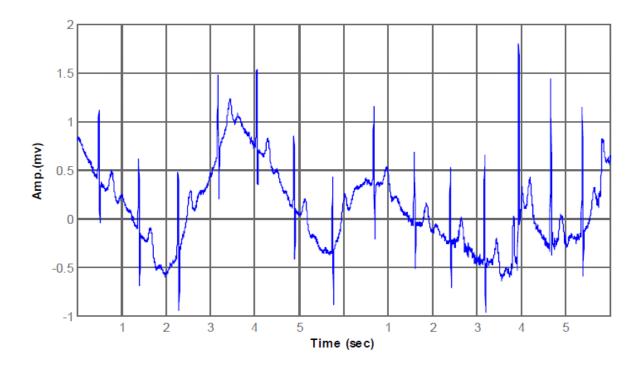

| Figure 2.4 ECG signal with baseline wandering noise                                         | 40 |

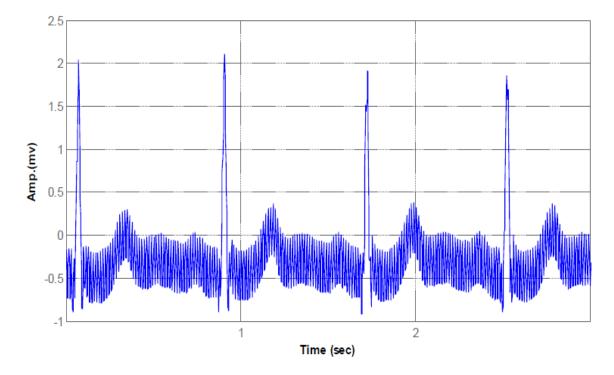

| Figure 2.5 Nominal 50 Hz frequency Power line interference added to ECG signal              | 41 |

| Figure 2.6 electromyography (EMG) signals                                                   | 42 |

| Figure 2.7 Motion artefacts contaminating the ECG signal                                    | 43 |

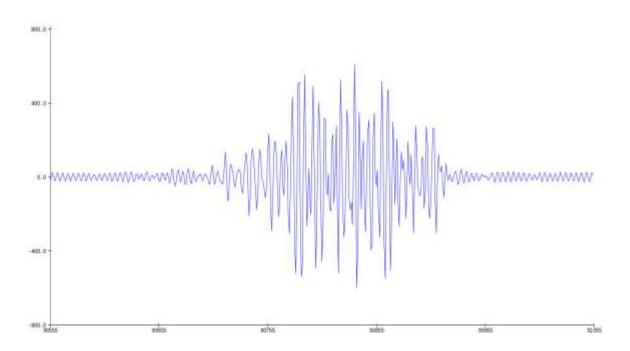

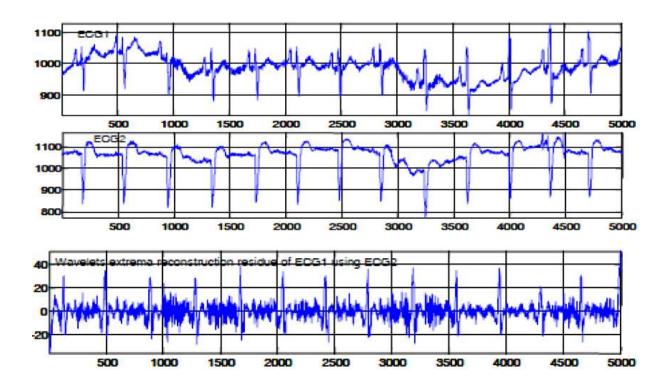

| Figure 2.8 Baseline derivative reductions by wavelet filtering                              | 51 |

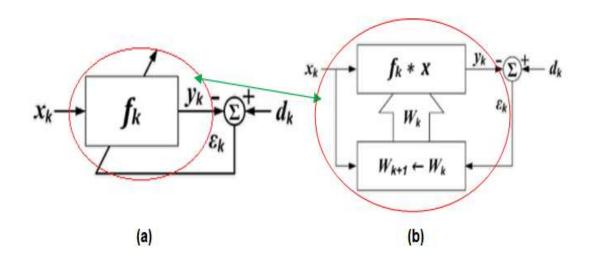

| Figure 2.9 Adaptive-filter structure (a): linear filter structure (b): adaptation algorithm | 54 |

| Figure 2.10 IIR filter operation                                                            | 58 |

## Chapter III: SoC platforms based on programmable circuits

| Figure 3.1 Xilinx FPGAs Organization                 | 74 |

|------------------------------------------------------|----|

| Figure 3.2 Simplified architecture of a "Slice"      | 75 |

| Figure 3.3 LUT configuration modes                   | 76 |

| Figure 3.4 Generic design flow                       | 77 |

| Figure 3.5 Zynq overall views                        | 78 |

| Figure 3.6 Zynq Design Flow Steps                    | 79 |

| Figure 3.7 Application Processing Unit Structure     | 80 |

| Figure 3.8 Structure of the PL                       | 81 |

| Figure 3.9 Xilinx Synthesis flow                     |    |

| Figure 3.10 Implementation Flow                      | 86 |

| Figure 3.11 verification steps                       |    |

| Figure 3.12 Back-Annotation Processes                |    |

| Figure 3.13 simulation procedure of a modelsim SoC   | 91 |

| Figure 3.14: Design flow for Xilinx System Generator |    |

## Chapter IV: ECG de-noising and FPGA implementation

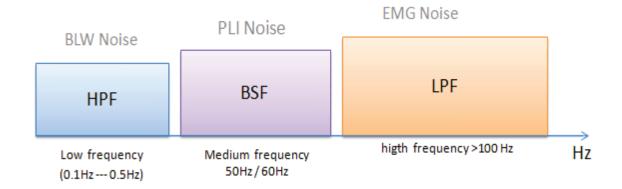

| Figure 4.1 Filter types corresponding to major noises' frequency                          | 99     |

|-------------------------------------------------------------------------------------------|--------|

| Figure 4.2 Diagram of the proposed method                                                 | 104    |

| Figure 4.3 Simulink FDA Tools model used in the first stage                               | 106    |

| Figure 4.4 Simulink FDA Tools model used in the last stage                                | 107    |

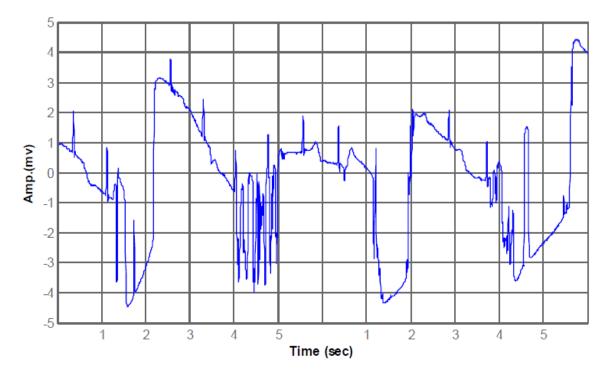

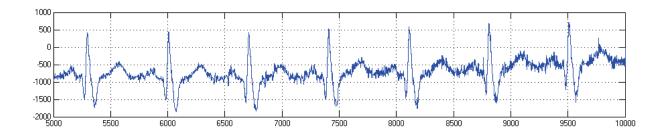

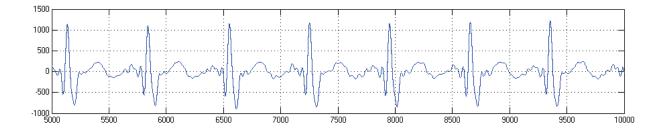

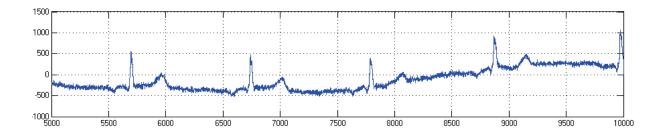

| Figure 4.5 Raw ECG signal Mixed with BLW and PLI Noises                                   | 110    |

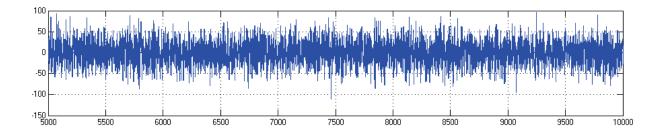

| Figure 4.6 Additive WGN with SNR =-27.42 dB                                               | 110    |

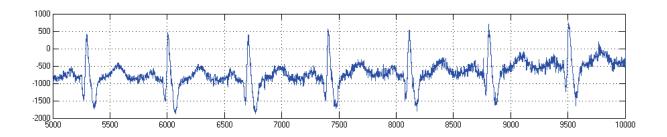

| Figure 4.7 Noisy ECG signal                                                               | 110    |

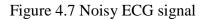

| Figure 4.8 ECG signal without BLW Noise                                                   | 110    |

| Figure 4.9 ECG signal without PLI Noise                                                   | 111    |

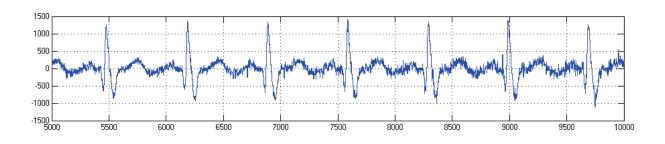

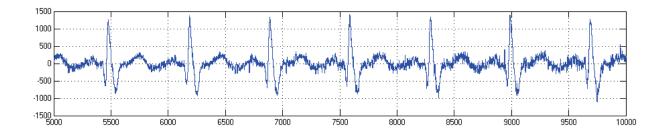

| Figure 4.10 Filtered ECG signal (without EMG Noise)                                       | 111    |

| Figure 4.11 Diagram of the proposed method                                                | 113    |

| Figure 4.12 The Kaiser and Rectangular performances                                       | 115    |

| Figure 4.13 Steps of de-noising ECG signal using the H-B-L configuration                  | 118    |

| Figure 4.14 output signals resulted from the cascaded filter with different configuration | ons119 |

| Figure 4.15 Raw ECG signal before filtration                                              | 121    |

#### List of Figures

| 121      |

|----------|

| 125      |

| 128      |

| 129      |

| 139      |

| 130      |

| 131      |

| 132      |

| 133      |

| R filter |

| 134      |

| suit     |

| 135      |

|          |

### List of tables

## Chapter I: Anatomy and functionality of the human heart

Chapter II: A Review on Biomedical ECG signal Filtering and Analysis

## Chapter III: SoC platforms based on programmable circuits

| Table 3.1 part of the market for different manufacturers | 72 |

|----------------------------------------------------------|----|

| Table 3.2 Technologies used by different manufacturers   | 73 |

## Chapter IV: ECG de-noising and FPGA implementation

| Table 4.1 Adjustable windows parameters    1                                               | 101 |

|--------------------------------------------------------------------------------------------|-----|

| Table 4.2 First stage results of several windows using SNR and MSE parameters1             | 08  |

| Table 4.3 The last stage results of de-noising performance of several configurations using |     |

| SNR and MSE1                                                                               | 109 |

| Table 4.4 the results of the de-noising performance of several positions using SNR and MS  | E   |

| parameters1                                                                                | 116 |

| Table 4.5 Confirmation effects of the de-noising performance of a proposed method for PT   | Έ   |

| diagnostic database for different diseases1                                                | 120 |

| Table 4.6 comparison of proposed cascaded fir filter design with existing work             | 122 |

## الملخص

تحتوي هذه الرسالة على دراسة شاملة لإشارة مخطط كهربية القلب ، حيث تتضمن عدة فصول مترابطة تحتوي على سلسلة من المعلومات عن قلب الإنسان. ركزت الدراسة على إز الة الضوضاء باستخدام طريقة مرشح متسلسل لثلاثة مرشحات FIR. في المقالة الأولى ، تتضمن الطريقة دراسة تنقية إشارة ECG عن طريق اختيار النوافذ جنبًا إلى جنب مرشحات FIR. في المقالة الأولى ، تتضمن الطريقة دراسة تنقية إشارة ECG عن طريق اختيار النوافذ جنبًا إلى جنب مع أجزاء المرشح المتتالية. تحتوي المقالة الثانية على طريقة دراسة تنقية إشارة الحصوماء باستخدام طريقة مرشح متسلسل لثلاثة مع أجزاء المرشح المتتالية. تحتوي المقالة الثانية على طريقة دراسة تنقية إشارة ECG عن طريق اختيار النوافذ جنبًا إلى جنب مع أجزاء المرشح المتتالية. تحتوي المقالة الثانية على طريقة دراسة ترشيح إشارة وECG عن طريق تحليل التباين الناتج عن تبادل مواضع مرشحات الفلتر المتتالي بواسطة ANOVA. أسفرت كلتا الطريقتين عن نتائج مبهرة مقارنة بالعمل الأخير السابق. وهكذا توصلنا إلى أن هاتين الطريقةين أعطتا نتائج متكافئة بغض النظر عن الطريقة المستخدمة . لقد قدمنا أيضًا المتدالي ألى أن هاتين الطريقة يلي محلك التناج متكافئة بغض النظر عن الطريقة المستخدمة الأخير ألصابق. وهكذا توصلنا إلى أن هاتين الطريقتين أعطتا نتائج متكافئة بغض النظر عن الطريقة المستخدمة . لقد قدمنا أيضًا امتدالي لما محل لتسخير ZedBoard النظر عن الطريقة المستخدمة . أيضًا المدادًا للمساهمة في تضمين FPGA من خلال تسخير ZedBoard الأنظمة الهحمولة.

كلمات مفتاحية : ECG ، التتالي ، FIR، ضوضاء ، SNR، الفافذة ، قاعدة بيانات PTB ، التباين ، التشخيص.

#### Abstract

This thesis contains a comprehensive study of the electrocardiogram signal, as it includes several interrelated chapters containing a series of information on the human heart. The study focused on noise removal using a sequential filter method of three FIR filters. In the first article, the method involves the study of electrocardiogram signal purification by selecting windows combined with successive filter portions. The second article contains the method of studying ECG signal filtering by analyzing the variance resulting from the exchange of positions of the filters of the cascading filter by ANOVA. Both methods yielded impressive results compared to previous recent work. Thus, we concluded that these two methods gave equivalent results, regardless of the method used. We have also provided an extension of the contribution to FPGA embedding by harnessing the Matlab Simulink SG, connected to the XILINX ZedBoard, the magnificence of this contribution having received remarkable results of great interest in the field of embedded systems.

Keywords: ECG, Cascade, FIR, Noise, SNR, MSE, Window, PTB database, Disparity, Diagnostic.

#### Résumé

Cette thèse contient une étude complète du signal de l'électrocardiogramme, car elle comprend plusieurs chapitres interdépendants contenant une série d'informations sur le cœur humain. L'étude s'est concentrée sur l'élimination du bruit à l'aide d'une méthode de filtrage séquentiel de trois filtres FIR. Dans le premier article, la méthode consiste à étudier la purification du signal d'électrocardiogramme par sélection de fenêtres combinées à des portions de filtre successives. Le deuxième article, contient la méthode d'étude du filtrage du signal ECG en analysant la variance résultant de l'échange de positions des filtres qui composent le filtre en cascade par ANOVA. Les deux méthodes ont donné des résultats impressionnants par rapport aux travaux récents précédents. Ainsi, nous avons conclu que ces deux méthodes donnaient des résultats équivalents, quelle que soit la méthode utilisée. Nous avons également fourni une extension de la contribution à l'embarquement FPGA en exploitant le Matlab Simulink SG, connecté au XILINX ZedBoard, la magnificence de cette contribution ayant reçu des résultats remarquables d'un grand intérêt dans le domaine des systèmes embarqués.

*Mots clés* : ECG, Cascade, FIR, Bruit, SNR, MSE, Fenêtre, Base de données PTB, Disparité, Diagnostic.

Cardiovascular disease is the most common cause of death worldwide, heart rhythm disorders and related pathologies are rising. They result in a heart that beats too slowly, too fast or in a disorderly manner; and often require specific equipment (pacemakers, defibrillators).

Therefore, the diagnosis of these diseases is a vital task. To perform this procedure, several tools are used, including the electrocardiogram (ECG).

The ECG is the oldest and most widely available physiological test. It helps to identify cardiovascular diseases. However, in a real scenario, the quality of the signals measured by this type of device can be degraded by different sources of interference. The signal is affected by several different types of noise, such as electromyography (EMG) noise, high-frequency noise (additive Gaussian white noise and power line interference (PLI), and low-frequency noise (wandering of the baseline), during its acquisition and transmission.

The signal's nonlinear and non-stationary nature and the noises that affect it constitute an obstacle. The need to overcome these obstacles is the cause of various approaches and techniques for its treatment; one of the approaches used for ECG signal processing is filtering.

ECG signals are generally in analogue form; these signals transform a processing chain (amplification, sampled and quantified) to pass from the continuous domain, output from a sensor, to the discrete domain, interpretable by a machine [1]. Signal operations in the discrete domain are much more efficient with the rapid improvement in information technology. The most common method of recovering the desired information from a signal is filtering. The filters are in the continuous domain, with analogue signals, or in the discrete domain, with digital signals.

FIR (Finite Impulse Response) filters are typically chosen for applications where the linear phase is essential, and a decent amount of memory and computational performance is available. They are widely used in biomedical signal enhancement applications. Their all-zero structure (discussed below) ensures they never become unstable for any input signal, giving them a distinct advantage over IIR filters.

Multiple algorithms for filtering a signal have advantages and disadvantages in the temporal, frequency and phase planes. Several filtering approaches dedicated to the ECG signal have

been studied in the literature. Some of them use classical filtering approaches such as analysis by discrete wavelet transforms (DWT) [2-3], the principle of smoothing by the use of the Savitzky-Golay filter for the step of preprocessing [4], adaptive filtering in [5, 6] and digital filter in [7]. Others use advanced methods based on artificial intelligence and deep learning [8] or deep factor analysis to eliminate a noise signal with Gaussian distribution proposed by Ge Wang et al. [9].

The filter is made analogically by electronic circuits consisting mainly of passive elements (resistors, capacitors, and inductors) and active elements (transistors or integrated circuits operational amplifiers) or digital circuits using lap computers, a CPU and memory. Digital filters are, in most cases, a part that integrates a real-time on board device.

The notion of real-time embedded operation leads us to introduce progress on the integration capabilities of electronic circuits, which have opened up new perspectives for real-time signal processing on embedded systems. On the one hand, specific processors can commonly perform billions of operations per second, and on the other hand, reprogrammable components comprise several billion logic gates. These circuits make it possible to carry out applications with performance in terms of constantly increasing processing speed. [10].

In this context, the Field Programmable Gate Array (FPGA), with its great integration and reconfiguration capabilities, make it a critical component for rapidly developing prototypes through the use of development environments such as Quattus from Intel-Alter and Vivado from Xilinx intended even for non-experts.

This thesis aims to study ECG signal noise removal methodologies based on FPGA application. The thesis is organized as follows:

First, it provided several pattern recognition, human heart function and anatomy methodologies, ECG databases, and resources.

• In Chapter 2, discusses ECG signal filtering techniques emphasizing improving the generalization ability.

• Chapter 3 includes SoC for the embedded system. In this chapter, we give particular importance to programmable circuits.

• Chapter 4 covers the purpose of this thesis, where we adopt the windows selection algorithm, modifying the optimization criterion to select a digital filter design with greater generalization.

This chapter comprehensively explains the published articles [11] and [12] results and then the results of the extension of the embedded system using an FPGA application based on the XILINX DIGILENT board.

#### References

[1] Joseph D. Bronzino, Donald R. Peterson, "Biomedical Engineering Fundamentals", 2nd Edition, Boca Raton CRC Press, Décembre 2014, doi.org/10.1201/b15482.

[2] Ranjeet Kumar et al., ''Dual-Tree Sparse Decomposition of DWT Filters for ECG Signal Compression and HRV Analysis'', *Springer Augmented Human Research volume 6:2021*, DOI:10.1007/s41133-020-00041-z.

[3] V Vijendra, Meghana Kulkarni, 'ECG signal filtering using DWT haar wavelets coefficient techniques', *International Conference on Emerging Trends in Engineering, Technology and Science (ICETETS), February 2016, Pudukkottai, India* DOI: 10.1109/ICETETS.2016.7603040.

[4] S. Hargittai, 'Savitzky-Golay least-squares polynomial filters in ECG signal processing'', *Computers in Cardiology 32:763 2005, DOI: 10.1109/CIC.2005.1588216*

[5] Mardi Turnip et al.'' Extraction of ECG signal with adaptive filter for hearth abnormalities detection'', *Journal of Physics: Conference Series, Volume 1007, International Conference on Mechanical, Electronics, Computer, and Industrial Technology 6–8 December 2017, Prima, Indonesia.*

[6] SuranaiPoungponsriXiao-HuaYu, '' An adaptive filtering approach for electrocardiogram (ECG) signal noise reduction using neural networks'', NeurocomputingVolume 117, 6 October 2013, Pages 206-213, DOI: 10.1016/j.neucom.2013.02.010

[7] Shadnaz Asgari , Alireza Mehrnia, "A novel low-complexity digital filter design for wearable ECG devices", PLoS ONE volume 12, DOI:10.1371/journal.pone.0175139

[8] Yi-Wei Lee et al, " Prospectively versus Retrospectively ECG-Gated 256-Slice CT Angiography to Assess Coronary Artery Bypass Grafts Comparison of Image Quality and Radiation Dose", *PLoS ONE volume*, DOI: 10.1371/journal.pone.0049212

[9] Ge Wang et al, '' ECG signal de-noising based on deep factor analysis'', *Biomedical Signal Processing and ControlVolume 57, March 2020*, DOI:10.1016/j.bspc.2019.101824,

[10] Debyo Saptono, '' Conception d'un outil de prototypage rapide sur le FPGA pour des applications de traitement d'images'', *Thèse de doctorat université de Bourgogne, 2011. France*

[11] Abdenour, Allali, and Arres Bartil. "ECG De-noising based on the Selection of CascadedFIR Filter Configuration." Serbia and Montenegro IEEE MTT-S Chapter Activities, Microwave Review - Vol. 26, No. 2, December 2020.

[12]. Abdenour Allali, Arres Bartil, Lahcene Ziet. "Revealing and evaluating the influence of filters position in cascaded filter: application on the ECG de-noising performance disparity *Indonesian Journal of Electrical Engineering and Computer Science* Vol. 21, No. 2, pp. 829~838, February 2021

#### **Chapter I: Anatomy and functionality of the human heart**

#### **1.1Introduction**

Before looking into the details of advanced ECG processing and FPGA implementation, it is essential to understand the physiology of the heart and how to measure the electrical activity of the heart's conduction system. This is important because the following chapters address noise suppression issues in ECG signals and propose new algorithms to reduce ECG signal distortion. Therefore, a brief introduction to cardiac physiology and anatomy is included in this chapter.

The different patterns in which experts analyze the electrical activity of the heart's conduction system are presented. Monitoring devices such as Holter Monitor are introduced to understand the traditional path with new technology applied to the recorded signal before it reaches the hands of experts. The PTB diagnostic electrocardiogram database is presented with some details, which in turn have achieved the announced contributions in the last chapter of this thesis. Finally, most challenges and problems while obtaining an ECG signal are presented and discussed.

#### 1.2Cardiovascular system

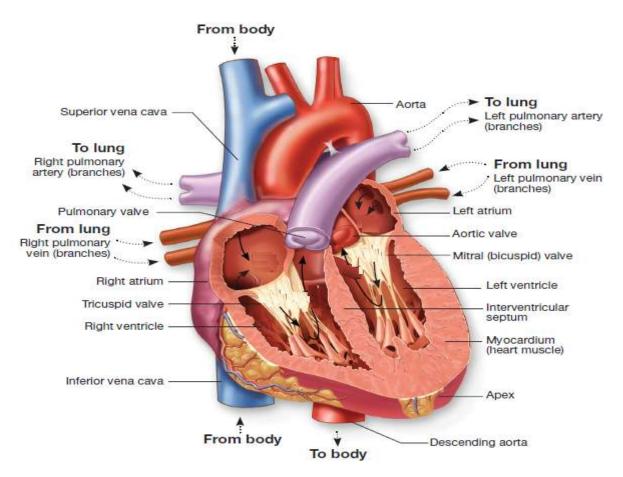

The heart is a muscular organ pump that pumps oxygenated blood to the whole body through the circulatory system. The heart is located in the medial thoracic cavity to the lungs and posterior to the sternum. The heart has four chambers: the right and left atria and the right and left ventricles. Several AV and AV nodes are also seen in the heart. Appearance. Figure 1.1 represents the blood flow diagram of the human heart. The left and right ventricles are located in the heart's lower chamber, while the right and left atria are located in the upper chamber of the heart. The atria are connected to the ventricles by fibrous, non-conductive tissue that keeps the atria electrically isolated from the ventricles.

The circulation of blood through the heart is divided into two phases: systole and diastole. Systole is the period of contraction of the ventricular myocardium, while diastole is the period of dilation of the ventricular cavities of the heart [1]. It receives impure and deoxygenated blood through the veins and pumps it to the lungs for purification. Deoxygenated blood is obtained through large veins such as the superior and inferior vena cava and flows into the

#### Chapter I: Anatomy and functionality of the human heart

right atrium. The right atrium contracts and pushes blood into the right ventricle. At this time, the ventricle is tightened, and the pumping efficiency, i.e. contraction, is maximized. The blood then travels from the right ventricle to the lungs for purification. The left atrium receives purified blood from the lungs. During atrial systole, the purified blood in the left atrium goes into the left ventricle through the mitral or bicuspid valve. The left ventricle contracts and pumps pure blood to the rest of the body through the aortic valve and aorta [2], [3]. During the ventricular diastolic period, oxygenated blood reaches the left ventricle from the left atrium by opening the mitral valve, and deoxygenated blood reaches the right ventricle from the right atrium by opening the tricuspid valve. In the systolic period of the heart ventricle, the oxygenated blood is pumped out from the left ventricle to the body by opening the aortic valve through the aorta, and the deoxygenated blood goes to the lungs from the right ventricle by opening the semi lunar valve through the pulmonary artery. The heart's function is to regularly contract and pump blood to the lungs for oxygen and then pump this oxygenated blood for general circulation. This perfect rhythm is continuously maintained by the electrical signals generated by the pacemaker.

Figure 1.1: movements of the walls and valves (arrows)

Made up of the heart and vessels (arteries and veins), the function of the cardiovascular system is to distribute to organs through the blood oxygen and nutrients essential to their life while eliminating waste.

#### 1.2.1 Arterial and venous circulation

The blood circulates within a network made up of "pipes" in figure 1.1, with calibres perfectly suited to their functions

1. Arteries, from the large aorta (2.5 centimetres in diameter) to small arterioles (no more than 2 millimetres), carry oxygen-laden blood from the heart to the organs.

2. The thin "like hair" capillaries ensure blood circulation inside each organ.

3. The veins bring the carbon dioxide-laden blood back to the heart.

#### 1.2.2 The heart of the human body

The heart, enveloped in the pericardium, is located in the anterior mediastinum between the two lungs, on the left diaphragmatic dome, behind the sternum and the anterior costal grill and in front of the posterior mediastinum, especially the oesophagus.

Responsible for blood circulation, the heart is a muscle, reddish-brown, which weighs about 250 g in adults: It has the shape of a triangular pyramid with the top at the bottom, to the left and in front; the base looks up, back and right; its central axis is oblique down, forward and to the left.

The three faces are anterior, inferior and left lateral.

Two deep furrows cross them:

1. The atrioventricular groove, in the plane perpendicular to the major axis of the heart, separates the atrial mass behind from the more anteroinferior ventricles,

2. The inter-ventricular groove, then the inter-auricular groove perpendicular to the previous one. It corresponds to the plane of separation between the right heart and the left heart. The furrows contain fat and the main branches of the coronary vessels.

The heart (Figure 1.1) is a hollow organ made up of the right heart and left heart, completely separate. The atria are separated by a septum called the inter- atrial septum and the ventricles by the inter-ventricular septum.

#### 1.2.3 Cardiovascular physiology

The heart can be considered as a double muscular pump (right heart and left heart):

1. Essentially driven by the myocardium of the right and left ventricles,

2. Functioning thanks to the nodal tissue (where cardiac automatism is born) and to the coronary blood circulation (providing oxygen and energy and evacuating cloudy waste),

3. Pulsing the blood synchronously in the pulmonary and systemic circulations, which feedback on its functioning,

4. Adapt the blood flow it produces to the organism's needs thanks to a nervous and humoral regulatory system.

#### **1.3 Functioning of the heart**

#### 1.3.1 The Cardiac mechanical activity

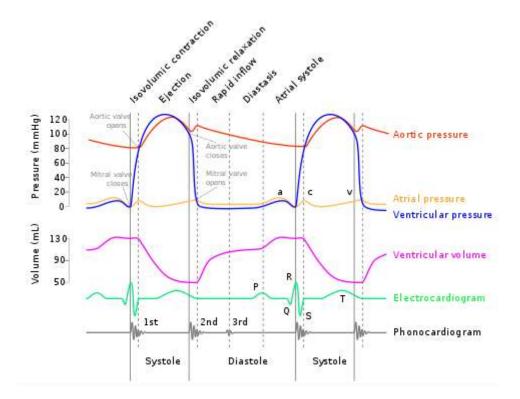

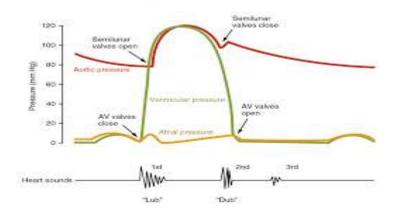

The heart propels blood through contractions of its muscle tissue called the myocardium. This cycle repeats itself constantly, and consists of three distinct phases see Figure 1.2

- Atrial systole: The contraction of the atria and the ejection of blood to the ventricles, the closing of the atrioventricular valves and the presence of a severe noise of the heart (represents 1/6 of the cycle).

- Ventricular systole: a contraction of the ventricles and the ejection of blood to the organs.

- closure of sigmoid or arterial valves (aortic on the left and pulmonary on the right) and the presence of acute heart noise (represents 1/6 of the cycle).

- Diastole: relaxation of all parts of the heart, passive filling (represents 2/3 of the cycle).

Figure 1.2 Wiggers diagram of the cardiac cycle.

Events of the cardiac cycle for left ventricular function, displaying adjustments in left atrial pressure, left ventricular pressure, aortic pressure, ventricular volume, and the electrocardiogram.

#### **1.3.2 Electrical activation of the heart**

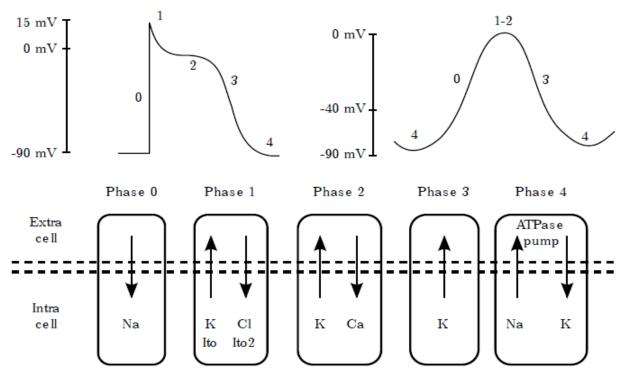

#### 1.3.2.1 Potential for rest and action

At rest, myocardial cells are "polarized" with a predominance of positive charges on the outside and negative charges on the inside.

If two microelectrodes connected to a galvanometer are placed one extracellularly and the other in a cell, a stable potential difference is registered, different according to the cell type, of the order of - 90 mV for a ventricular cell: it is the transmembrane resting potential (Vr).

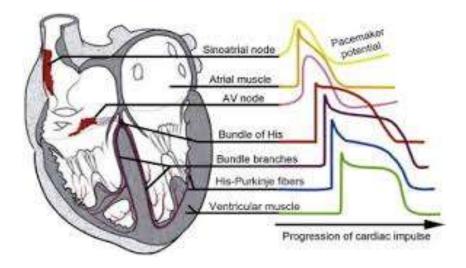

If the cardiac fibre is stimulated, an action potential in figure 1.3 appears, which reflects the variations in the transmembrane Potential as a function of time.

These variations result from ionic movements across cell membranes.

Figure 1.3 The Potentials of the nodal tissue.

In widespread heart, cells may be grouped into sorts: those from the SCS and the contractile cells. The first is accountable for the era of the electric impulse (rhythm city) and its conduction to the contractile cells, at the same time as the contractile cells are answerable for the pumping or mechanical function. Both cellular sorts are liable for the electromechanical link. Figure 1.4 for its miles proven the waveforms of the voltage or motion potential, and currents measured inside the cell membrane of a contractile cellular. Following the depolarization stages inside the equal Figure, observe that Na channels are activated after a cellular gets depolarizing cutting-edge, ensuing in an internet inward advanced manifested as segment zero of the AP.

Phase one begins with the outlet of speedy outward potassium cutting-edge.

Phase two or the AP's plateau segment results from an L-kind Ca cutting-edge that counteracts the outward K currents. With time, L-kind Ca channels are inactivated, and the plateau subsides. At the same time, the boom in calcium awareness acts as a cause for the discharge of greater Ca saved within the sarcoplasmic reticulum, which in flip offers contraction signs to the myocyte contractile elements, generating the contraction of the cellular.

Phase three is because of "behind schedule rectifier" outward K currents.

Phase four constitutes a steady, stable, polarized membrane because of voltage-regulated inward rectifiers. Compared to an atrial motion potential, ventricular AP has an extended duration, a better segment 2, a shorter segment three, and a more significant bad segment four.

Figure 1.4 The action potential in the cells

Top panel: on the left, the motion capacity in contractile cells, and the proper in SCS cell. Bottom panel: most important currents for the duration of the exceptional stages of Nachannel-based motion capacity [4].

Alternatively, the SCS cells can generate a spontaneous motion capacity by using T-kind Ca and K rectifier currents. These currents confer the volatile electric belongings of section 4, inflicting those cells to increase rhythmic spontaneous sluggish diastolic depolarization. Furthermore, once AP reaches –forty mV, L-kind Ca channels are activated, producing the slow upstroke of the motion capacity in those styles of cells (section 0).

There are 3 styles of SCS cells:

1. P cells, discovered primarily with inside the sinus node, are answerable for automaticity.

2. The Purkinje cells are discovered with inside the His package branches and are answerable for the short transmission of electrical impulses via the ventricles.

3. The transitional cells, with sluggish conduction velocity, are generally discovered among the P, Purkinje and contractile cells.2.1.5.2

#### 1.3.2.2 Automation

Cardiac automatism is the production by the nodal tissue of repetitive electrical activity, with each electrical impulse (action potential) causing the heart to contract. This electrical activity is produced by spontaneous ionic exchanges (slow diastolic depolarization) across the membrane of nodal tissue cells to reach the threshold potential that triggers the action potential. Then occurs a complete restoration (repolarization).

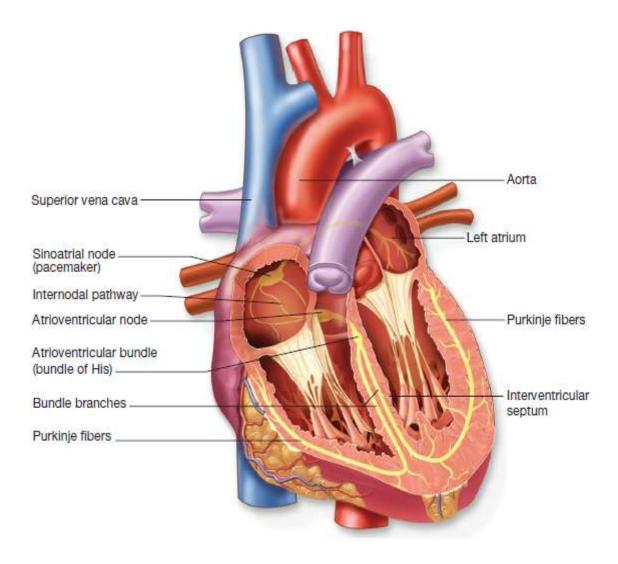

Physiologically, the cells of the sinus node in Figure 1.5 control the heartbeat, which is called sinus rhythm. The frequency of this rhythm is constantly modulated according to the body's needs by neuro -humoral regulation. (Acceleration under the effect of the sympathetic and catecholamines, slowing down under the impact of the parasympathetic).

In pathology, the origin of the automatism may not be sinus: either when an abnormal tachycardia occurs whose natural frequency exceeds that of the sinus node which is thereby inhibited, or when the sinus node is deficient, another cell group tissue then takes over to generate cardiac automatism.

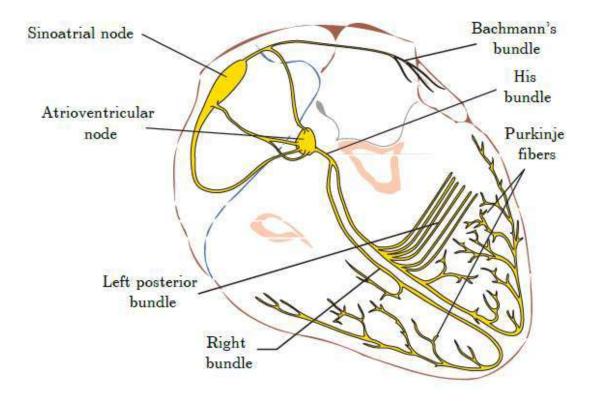

#### **1.3.2.3 Heart Conduction**

The action potentials generated by the nodal tissue are conducted at high speed to the cells of the common myocardium.

Physiologically, the nascent rhythm in the sinus node Figure 1.5 activates the atrial myocardium and reaches the atrioventricular node and the trunk of His bundle. This activity then reaches the right and left branches of the bundle of His, the Purkinje cells and finally the cells of the ventricular myocardium.

The interventricular septum is depolarized from left to right, then the ventricles from the endocardium to the epicardium. This "nodo-hissian" pathway is the only possible electrical passageway from the atria to the ventricle through the fibrous skeleton of the heart.

In pathology: conduction can be deficient at all levels leading to the risk of transient (syncope) or permanent (sudden death) arrest of cardiac activity.

Conversely, there may be additional conduction pathways between the atria and the ventricles called pre-excitation pathways that can expose patients with severe heart rhythm disturbances.

Figure 1.5 electrical conduction system of the heart

#### 1.3.2.4 Excitation and contraction coupling

At their level, the electrical excitation of the cells of the common myocardium by the nodal tissue causes significant ionic movements (especially calcium), triggering the shortening of contractile proteins (actin and myosin). As a result, all myocardial cells receive an electrical pulse briefly (6-8 / 100 seconds) to contract in a coordinated fashion and generate cardiac blood ejection.

This coupling is responsible for an electromechanical delay explaining that the ventricular diastole (see below) is contemporaneous with the "QRS" ECG complex of depolarization (see ECG), and the mechanical systole (see below) of the T wave (see ECG).

#### **1.3.2.5** Coronary circulation

The coronary blood circulation must ensure myocardial perfusion is adapted instantly to the heart's needs.

It is subject to specific constraints:

1. The heart is never at rest,

2. The myocardial oxygen extraction from the coronary arterial blood is almost maximal upon rest (greater than 60%).

As a result, the increase in the myocardial oxygen supply (during exercise), is done essentially by increasing the coronary blood flow and not the oxygen extraction; the ventricular systolic contraction "crushes" the coronary circulation, which rests.

#### 1.3.2.6 Coronary blood flow

This is the amount of blood delivered to the myocardium per minute. Its increase during exercise, thanks to complex regulation, is significant since it can be multiplied by 3 or 4 compared to rest (concept of coronary reserve). This increase ensures increased myocardial metabolic requirements (oxygen and substrates) during exercise. The regulation of coronary blood flow depends on many hemodynamic and neuro-humoral parameters, including endothelial secretions (N0 in particular).

#### 1.3.2.7 Myocardial metabolism

It is primarily aerobic (consumes oxygen). In clinical practice, this myocardial oxygen consumption (MVO2) can be assessed by the product heart rate (F) multiplied by systolic arterial pressure (PAS) because the variations of this MVO2 are well correlated with those of this product.

The substrates used are mainly fatty acids (65%), glucose (20%), and lactates (15%). It is strongly oriented towards the production of energy necessary for the activity of the heart's contractile proteins.

#### 1.3.2.8 Myocardial ischemia and necrosis

Insufficient blood supply to a myocardial area compared to requirements causes ischemia, which generates symptoms (see angina) or complications.

If this ischemia is profound and / or tasting, the myocardial cells will be destroyed in the affected area. This is myocardial ischemic necrosis.

#### 1.4 Cardiac cycle

The above-described routine electrical activity generates mechanical activity of the heart, dominated by contraction and then relaxation of the ventricles (contraction of the atria has only a limited impact on normal heart function). The succession of ventricular systole and ventricular diastole forms a cardiac cycle.

#### 1.4.1 Ventricular systole

The contraction of the two ventricles is synchronous and lasts about a third of a second at rest. Its onset coincides with the closure of the atrioventricular valves, followed by the opening of the aortic valve and pulmonary sigmoid.

During systole, intraventricular pressures (Figure 1.6) increase sharply, allowing blood to be ejected from the right ventricle to the pulmonary artery and blood from the left ventricle to the aorta.

With the atrioventricular valves closed, there is no backflow to the atria.

The quality of systolic blood ejection depends on:

1. The contractility of the ventricular myocardium, an intrinsic property of myocardial cells which deteriorates in heart disease,

2. The ventricular preload,

3. Ventricular after load.

The ventricular contraction decreases rapidly at the end of systole, and then diastole appears.

Figure 1.6 different times and evolution of intracavitary pressures

The pressure curves of the left atrium, ventricle, and aorta are superimposed (for the right heart, the diagram is identical except for the pressure levels).

Abbreviations: Ao: aorta; OG: left atrium; LV: left ventricle.

Between the closing of the mitral valve and opening of the aortic valve = Isovolumic Contraction phase.

4. Between opening and closing of the aortic valve: Ejection phase.

5. Between the closing of the aortic valve and opening of the mitral valve: Isovolumic Relaxation phase.

6. Between the mitral opening and closing: ventricular filling.

7. Between B1 and B2 are the isovolumic contraction and ejection phases.

#### 1.5 Electrocardiogram ECG

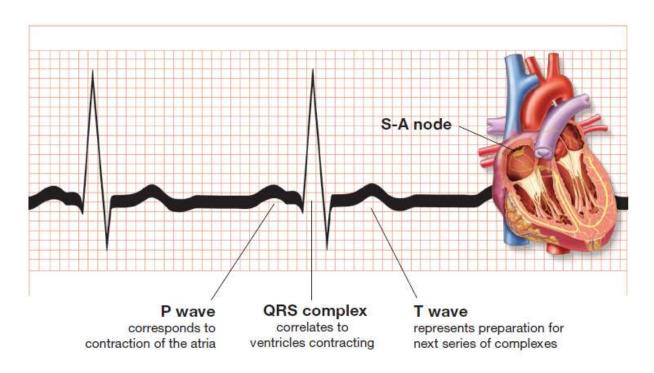

The ECG signal represents the heart's electrical activity and is arguably the most widely used diagnostic technique for cardiac pathologies. The ECG is a non-stationary random signal structured by the succession of waveforms and intervals (P, Q, R, S, and T).

Any morphological or temporal modification of its events (or chronic) constitutes a cardiac pathology. For example, changes in rhythm or frequency are cardiac arrhythmias (fatal diseases) and are the subject of this work.

The history of the ECG is around the 1880s when Augustus Waller and E Marey De Silva [5, 6] showed the possibility of skin-based monitoring of the heart's electrical activity. British physiologists John Burden Sanderson and Frederick Page recorded this activity with the capillary electrometer a few years earlier [7]. They were shown to be composed of two phases (later called QRS and T). In 1887 Augustus D. Waller published the first human electrocardiogram, while in 1895; Willem Einthoven defined the five deflections P, Q, R, S and T [8]. He used the string galvanometer in 1901 and published the first classifications of pathological electrocardiograms in 1906. In 1924 he won a Nobel Prize for his work on electrocardiography.

An electrocardiogram (ECG) is a graphical representation of the heart's electrical activity. This electrical activity is linked to variations in the electrical Potential of cells specialized in contraction (myocytes) and cells specialized in the automatism and conduction of impulses. Electrodes collect it on the surface of the skin.

- 1. The ECG is the paper trace of electrical activity in the heart.

- 2. The ECG machine is the device for doing an ECG machine.

- 3. The electro-cardio-scope, or scope, is a device that displays the waveform on a screen.

Figure 1.7 electrical system in the heart

The electrocardiogram, known as an ECG, is a dimension of the electric hobby of the heart (see Figure 1.8). This can provide the medical doctor statistics approximately the fitness of the heart, especially the myocardium.

Figure 1.8 an electrocardiogram ECG wave's document of the electric sign because of its movements via the conduction machine of the coronary heart. This sign stimulates the chambers of the coronary heart to an agreement and loosens up with inside the right sequence.

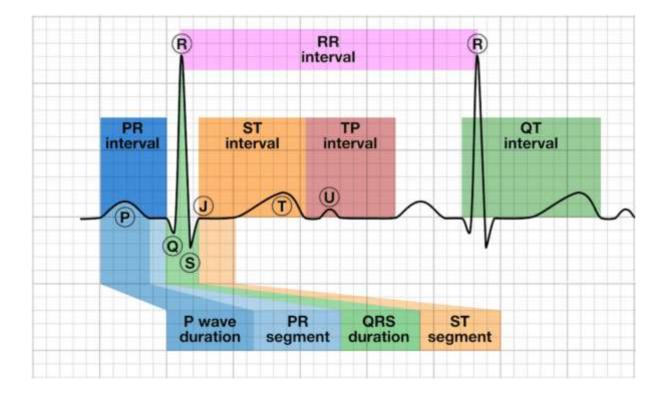

## **1.5.1 ECG Waves and Intervals**

The recorded trace, called an electrocardiogram (ECG), presents a characteristic appearance; its deformities are a sign of abnormalities in the functioning of the heart. Any interpretation of the ECG refers to the shape and wave width characteristics of the normal ECG signal shown in Figure 1.9.

**P** wave: It corresponds to the depolarization of the atria from the sinus node to the atrioventricular node. It can be positive or negative; with around 90 ms. This is the wave that precedes the QRS complex. Usually, it is difficult to see on the ECG, especially under noisy conditions.

**QRS complex:** It corresponds to the ventricular depolarization preceding the mechanical effect of contraction. It has the most significant amplitude of the ECG signal and is composed of three contiguous waves that follow the P wave; a wave called Q first of negative amplitude,

a wave called R positive in a normal ECG and finally, the 'S wave, which is negative. The normal duration of the QRS complex is between 85 and 95 ms.

**T wave:** It corresponds to the repolarization of the ventricles; it can be positive, negative or biphasic. This is the wave that follows the QRS complex after returning to the isoelectric line (except for specific pathology); its amplitude is lower than that of the QRS complex.

PR Interval: The PR interval, which has a duration between 0.14 to 0.2 seconds measured

Figure 1.9 Electrocardiogram ECG trace

Between the onset of the P wave and the onset of the QRS complex, that is, the time between depolarization of the atria and the AV node. This time is required for an electrical impulse to pass from the sinus node to the ventricles, and it is used for detecting arrhythmia and heart rate variability.

**ST-segment:** Or the duration of complete stimulation of the ventricles. It is the interval during which the ventricles remain in an active depolarized state. This is the time between the end of the S wave and the start of the T wave.

**PQ interval:** This is the time interval between the onset of depolarization of the atria and that of the ventricle. This is the propagation time of the electrical impulse from the sinus node to the ventricles. It is measured between the onset of the P wave and the onset of the QRS complex.

**QT interval:** This interval corresponds to the time of ventricular systole, which goes from the start of excitation of the ventricles until the end of their relaxation. This is the time between the onset of the QRS complex and the end of the T wave.

#### 1.5.2 Derivatives

The ECG signal records the heart's electrical activity by electrodes on the body's surface. Depending on their location, there are different derivations. The standard ECG is recorded on 12 leads (six limb leads and six precordial), with a paper speed of 25 mm per second and an amplitude of 10 mm at 1 mV. In what follows, we will represent the different standard leads of the clinical ECG and the ambulatory Holter recording, the terminology of waves and intervals used for the analysis of the ECG, and the different rhythm and cardiac conduction disorders. With details, the various artefacts visible on the ECG during recording.

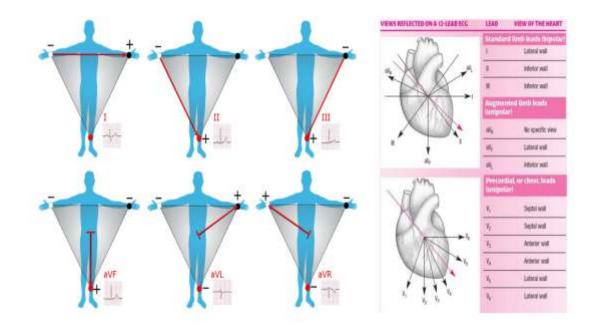

#### **1.5.2.1** Three bipolar leads (or standard leads)

Bipolar or so-called standard leads were proposed by Einthoven [9] at the start of the twentieth century and are still used today. They allow the study of the heart's electrical activity on the frontal plane. These three signals are the potential difference between distant points on the body.

We distinguish:

1. Lead I (DI): Bipolar measurement between left and right arm.

$$DI = VL - VR \tag{1.1}$$

2. Lead II (DII): Bipolar measurement between left leg and right arm.

$$DII = VF - VR \tag{1.2}$$

Lead III (DIII): Bipolar measurement between left leg and left arm.

$$DIII = VF - VL \tag{1.3}$$

Where VR corresponds to the Potential of the right arm, VL corresponds to the Potential of the left arm, and VF corresponds to the Potential of the left leg. The right leg is connected to the mass. The resulting vectors then form an equilateral triangle called the Einthoven triangle as shown in Figure 1.10.

Figure 1.10 The derivations of Einthoven

## **1.5.2.2 Three unipolar leads**

These leads also allow us to study the variation of electrical activity on the frontal plane. They were determined by Wilson [11] in 1934 and improved by Goldberger [12].

They allow us to obtain signals of greater amplitude. Each signal represents the difference between the Potential of one electrode and the average of the potentials collected by the other two electrodes. These derivations are known as aVR, aVL and aVF; where "a": augmented

voltage; that is to say, each potential collected is amplified. The "V" means this is a unipolar lead. "R", "L" and "F" is (Right, Left, Foot).

These leads are shown in Figure 1.10 bottom, and the voltages are calculated as follows:

$$aVR = VR - \frac{VL + VF}{2} \tag{1.4}$$

$$aVL = VL - \frac{VR + VF}{2} \tag{1.5}$$

$$aVF = VF - \frac{VL + VR}{2} \tag{1.6}$$

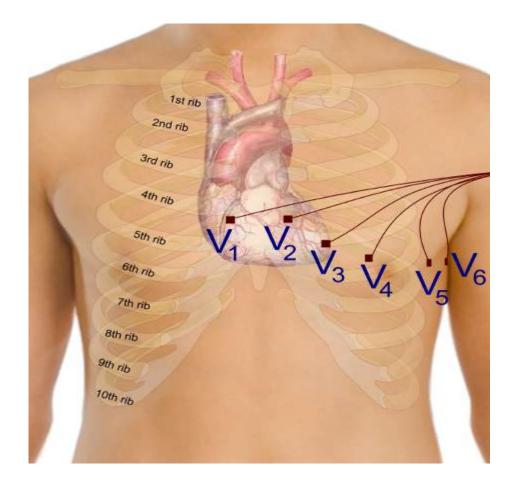

Six precordial derivations are unipolar derivations proposed by Wilson [13]. The exploration electrodes are placed near the heart at specific points on the thorax. They allow us to obtain the leads V1 to V6. Each Potential is calculated concerning the average value of the potentials VR, VL and VF. These leads will enableus to measure the heart's electrical activity horizontally. Figure 1.11 shows the location of the electrodes on the chest.

Figure 1.11 Unipolar precordial leads

### **1.6 ECG Monitoring Devices**

Several devices are used for ECG monitoring systems. These devices are typically mobile, wearable, and sensor-based. These ECG monitoring devices are smartphones, smartwatches, and handheld ECG monitors. Aljuaid et al. [14] assessed the importance and effectiveness of smartphone-based ECG monitoring devices on the frequency of clinic visits of patients who had AF ablation. This study proved that using the "ECG monitoring" application on smartphones leads to a large and significant reduction in inpatient visits to the clinic after surgery. Similarly, a few mobile monitoring devices integrate an Arduino microcontroller with various sensors, including an ECG sensor, these devices have been used to retrieve sensory data and display vital sign measurements and then alert with notification messages the location of the user to the health care provider if an abnormality is discovered [15]. A combination of microcontrollers such as Arduino with system-based smartphones has been developed to realize an intelligent healthcare system dedicated to elderly patients for home medical services [16]. The system incorporates an artificial bee colony (ABC) algorithm for detecting the R ECG peak. This system also detects various abnormalities (arterial hypertension, arterial hypotension, fever, tachycardia and bradycardia) and sends notifications in case of unexpected events.

#### **1.6.1 Traditional ECG Monitoring**

Other research has touched on traditional ECG monitoring setups in hospitals [17,18,19], homes, or remote ambulatory settings [15,16]. Screening devices can be linked to treatment devices or accessed wirelessly [20,]. In many research studies, immobile ad hoc (i.e., one-time) monitoring has been deployed to address various healthcare situations using different ECG sensors and monitoring types. The work of de Benini[20] designs a single-wire sensor for home remote monitoring; Yousef and Hau [15] use, in their mobile system (myVitalGear), an analogue heart rate sensor for general health monitoring. Rafik et al. [22] designed a device with three-lead wet electrodes for home health monitoring. Several researchers highlighted that ad hoc and non-mobile monitoring could reduce the burden of outpatient clinic visits and AF-related visits in the post-ablation period. In their study, Aljuaid et al. [21] show that traditional ad hoc home monitoring on smartphones can reduce the number of post-ablation patient visits by more than 50%. However, in ad hoc monitoring settings, patients may forget to perform monitoring tasks. In addition, it is vital for patients in critical health situations to have regular recurrent screenings. To solve this problem, some research work, episodic

#### Chapter I: Anatomy and functionality of the human heart

monitoring is proposed by performing pre-programming at intervals. For example, in the work of Hsieh and Len [16], an alarm function in the system to remind the patient to use the screening device is integrated. This approach saves medical resources and allows the elderly to take care of themselves, thereby promoting their health. Continuous monitoring is necessary for critical and life-threatening cases in traditional settings, especially in intensive care units. Many research studies have focused primarily on neonatal patients, for example, Bambang et al. [17] and Bouwstra et al. [18], who designed intelligent vest-based continuous monitoring systems for babies born prematurely in the neonatal ICU (NICU). Alternatively, for older adults who move, Ahmed et al. [23] used IoT-based technology for wireless sensor nodes positioned in intensive care and nursing wards to provide continuous ECG monitoring of patients with severe cases and then transmit the signal to distant doctors.

Accuracy in these situations is vital; therefore, a significant challenge encountered in continuous and intelligent critical care monitoring is the need to select an appropriate filtering technique; since ECG signals are noisy, which need a suitable amplifying approach should be used, given that the ECG signal is measured in millivolts.

#### 1.6.2 Real-Time ECG Monitoring

In some cases, cardiologists may recommend 24-hour Holter monitoring for patient monitoring. A Holter monitor is a 12-lead medical device that records the heartbeat and checks for unusual signs. It is usually uncomfortable to apply the Holter 12-lead device to the patient's body for 24 hours. Some attempts have improved the 24-hour Holter monitoring and utilized an adhesive patch that can be attached to the patient's body, reducing the number of required leads in a typical Holter. For instance, Karaoğuz et al. [24] used a BeyondCare device applied to the upper left upper region of the subject's chest beside the 12-lead Holter device simultaneously for palpitation assessment.Recent advancements in wireless ECG monitoring systems have produced a wide variety of real-time monitoring systems, ranging from wearable textile-based monitoring systems, such as intelligent shirts [25] and textile electrodes, to contactless [26] ECG monitoring systems. In real-time setups, patients can measure ECG signals while doing normal real-life activities [27]. This has allowed for more prompt assessment and medical intervention when necessary.

Furthermore, it substantially reduced the cost of healthcare expenses by lowering the number of hospital visits for traditional regular monitoring. For instance, Lee and Chung [25] designed an intelligent shirt that continuously measures ECG and acceleration signals

#### Chapter I: Anatomy and functionality of the human heart

remotely in a real-time setup for health monitoring. Bianchi et al. [28] proposed using T-shirts and bed sheets with sensor electrodes to measure ECG signals and other vital signs to assess sleep and respiratory problems in real-life settings. Bsoul et al. [29] designed Med Assist, a continuous, real-time, single-lead, wireless monitoring system to diagnoses leep apnea. On the other hand, the authors of [30,31] designed washable long-term wearable sensors for fitness and activity monitoring. Despite the advantages of continuous monitoring in real-time setups, it generates an abundant amount of ECG signal data, giving substantial signal noise and artefacts caused by abnormal physical activities. This problem has been highlighted by many researchers [25, 28]. This, in turn, emphasizes the need for noise filters and smart feature selection algorithms. Alternatively, episodic monitoring was adopted in several kinds of research to limit the causes of motion artefacts and constrain the amount of generated ECG signal data, allowing for easier processing and analysis. For example, Yoon and Gho [26] utilized a commercial contactless ECG monitoring device for remote home telemedicine. Their experiments considered pre-programmed and pre-planned 3-time intervals focusing on the patient's resting state and post-exercise state. Lee et al [32]. investigated a mobile cardiopulmonary rehabilitation system with a wireless Holter ECG to give real-time feedback during exercise in home settings.Unlike the pre-programmed continuous monitoring approach, some researchers have preferred to adopt signal sampling techniques for eventbased ECG monitoring.

Signal sampling algorithms convert continuous-time signals into discrete. Consequently, a considerable reduction is achieved in the number of processed signals and power consumption.

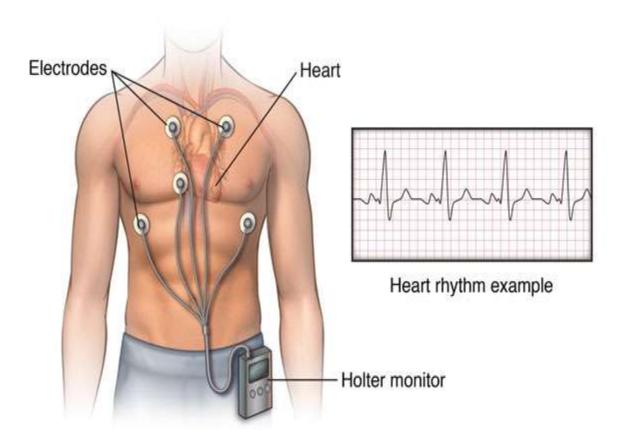

#### **1.6.2.1 HOLTER monitoring**

Holters are small electronics devices with electrodes, generally bylead wires [33]. Usually, they record 24 hours of ECG signals; however, some holders can register up to 7 days.

While wearing a holter, patients typically record their symptoms and function with their daily activities (see Figure 2.12). Activities that cause the electrodes to become loose orduring recording are exceptions. For instance, patients are asked to avoid taking a shower, swimming, or any activity causing an excessive amount of sweating. Once themonitor is returned, the data are analyzed in digital format using special analysis software.

Diaries are used to understand the correlation between analysis results on the one hand and activities and symptoms on the other hand.

Physicians decide to go for this recording to observe occasional cardiac arrhythmias that are difficult to identify in a shorter period because their symptoms areinfrequent. In this case, the short duration of monitoring can be inadequate.

Analyzing software is crucial when dealing with holter signals due to the long duration of the recorded signal. On average, more than 100.000 beats should be delineated and analyzed. Moreover, the presence of noises and artefacts in the HOLTER ECG signal is inevitable. Therefore, examining or browsing through such a long signal would be highly time-consuming.

Figure 1.12 Holter monitoring test

# **1.7 PTB Diagnostic ECG Database**

The ECG signals in this collection were collected using a prototype non-commercial PTB recorder with the following specifications:

- 16 channels (14 for ECG, 1 for respiration, 1 for mains voltage) for input

- $\pm 16$  mV Input voltage: offset voltage up to  $\pm 300$  mV compensation

- Input-resistance:  $100 \Omega$  (DC)

- Resolution: 16 bits with 0.5 micro-Volt/LSB (2000 A/D units per mV)

- Bandwidth: [0 1 kHz] (all channels sampling are synchronous )

- Noise: 10 µV max(pp), respectively 3 µV (RMS) with input short circuit

- Online skin registration resistance

- Recording noise level during signal acquisition

The database contains:

- 549 recordings of 290 subjects (age between 17 and 87, mean 57.2 years; 81 women, mean age 61.6 years, 209 men, mean age 55.5 years).

Each subject is represented by one to five records. There There aren't any topics numbered 124, 132, 134, or 161.

Each recording includes: 15 simultaneously signals measured: Frank's 3 ECGs (vx, vy, vz) with 12 conventional leads (i, ii, iii, avr, avl, avf, v1, v2, v3, v4, v5, v6).

Each digitized signal is 1000 samples/second, with resolution =16-bit over a range of  $\pm 16.384$  mV.

Recordings are available at sample rates up to 10 KHz

- The ECG header file (extension .hea) contain a detailed clinical summary, including age, sex, diagnosis and, if applicable, data on the medical history, medications and procedures, coronary pathology, ventriculography, echocardiography and hemodynamics

- The diagnostic classes of 268 subjects are summarized below:

| Diagnostic class             | Number of subjectc |  |

|------------------------------|--------------------|--|

| Myocardial infarction        | 148                |  |

| Bundle branch block          | 15                 |  |

| Myocardial hypertrophy       | 7                  |  |

| Dysrhythmia                  | 14                 |  |

| Cardiomyopathy/Heart failure | 18                 |  |

| Myocarditis                  | 4                  |  |

| Valvular heart disease       | 6                  |  |

| Healthy controls             | 52                 |  |

| Miscellaneous                | 4                  |  |

| Table 1.1 The PTB | diagnostic classes | [36] |

|-------------------|--------------------|------|

|-------------------|--------------------|------|

# 1.8 ECG signal problems during the Acquisition

## 1.8.1 Reversals lead

Lead switches are a common mistake when ECGs are made and can lead to wrong diagnoses. Common mistakes are:

-Left-right arm reversals lead to a negative complex in the lead I with a negative P wave in the lead I. They are one of the most common causes of right axis deviation on the ECG!

-Arm-foot switches lead to a very small or 'far field' signal in leads II or III.

-Chest lead reversals lead to inappropriate R wave progression (increase-decreaseincrease) and are often easily recognized.

Therefore any right axis or small signal in an extremity lead should be reason enough to check lead positioning. A previous ECG can be beneficial.

## 1.8.2 Artifacts

Artefacts (disturbances) can have many causes. Common causes are:

## -Movement

-Electrical interference

## 1.8.3 Filter settings

Although not a technical problem, filter settings influence the interpretation of the ECG.

To reduce electrical interference, ECG machines use two filters:

-A high pass filter reduces low-frequency noise. This filter reduces baseline drift on the ECG.

-A low pass filter reduces high-frequency noise, such as produced by chest and extremitymuscles and electrical interference from the power grid.

Depending on the purpose of the ECG these filters can be adjusted.

-In the monitor mode, the high pass filter can be set higher at 0.5-1.0 Hz and the bandstopfilter on 50 Hz. This is the most robust filter setting (the filter passes only a narrow frequency range). This setting is beneficial for rhythm monitoring, where noise can

bedistracting, and ST-segment interpretation is not very important. In this mode, pacemakerspikes are sometimes invisible while filtered out.

-In the diagnostic mode, the high-pass filter is set at 0.05 Hz and the low-pass filter at 50, 100 or 150.... Hz. This improves the diagnostic accuracy of the ST segment. However, on the downside, a baseline drift occurs more quickly.

## **1.9 Conclusion**

In this chapter, the idea of the cardiovascular system is introduced. This system culminates the arterial and venous circulation through the heart by its mechanical and electrical activity functions.

The preprocessing steps of the ECG signal are crucial for future segmentation and time-lapse analysis stages. Unfortunately, as we have seen, the recording conditions make the ECG noisy. Various noises associated with an ECG signal can alter clinical information to a greater or lesser extent, so it is essential to address them. In the next chapter, we will perform a detailed analysis of ECG signal noise and techniques for eliminating this noise.

### References

[1] L. Cromwell, F. J. Weibell, and E. A. Pfeiffer, *Biomedical Instrumentation and Measurements*.

PHI Learning Private Limited, New Delhi, 2009.

[2] U. R. Acharya, J. S. Suri, J. A. E. Spaan, and S. M. Krishnan, *Advances in Cardiac Signal Processing*. Springer, 2007.

[3] M. G. Khan, Rapid ECG interpretation, Third edition, 2003.

[4] Andrea Natale and Oussama Wazni. *Handbook of Cardiac Electrophysiology*. Informa Healthcare, 2007. ISBN-10: 1 84184 620 1.

[5] A Waller. An introduction to human physiology. New-York : Longmans Green, 1893.

[2] Regis A. DeSilva. George Ralph Mines, Ventricular Fibrillation and the Discovery of the Vulnerable Period1. Journal of the American College of Cardiology, vol. 29, no. 6, pages 1397 – 1402, 1997.

[6] J. Burdon Sanderson et F. J. M. Page. Experimental Results Relating to the Rhythmical and Excitatory Motions of the Ventricle of the Heart of the Frog, and of the Electrical Phenomena Which Accompany Them. Proc R Soc, vol. 27, pages 410–414, 1878.

[7] J Willis Hurst. Naming of the waves in the ECG, with a brief account of their genesis.

Circulation, vol. 98, no. 18, pages 1937–1942, 1998.

[8] Willem. Einthoven. Electrocardiogramme. In archives internationales de physiologie, pages 132–164, 1906.

[10] George B Moody, W Muldrow et Roger G Mark. A noise stress test for arrhythmia detectors. 1984.

[11] Frank N Wilson, Franklin D Johnston, A Garrard Macleod and Paul S Barker.

[12] Emanuel Goldberger. A simple, indifferent, electrocardiographic electrode of zero

Potential and a technique of obtaining augmented, unipolar, extremity leads. American Heart Journal, vol. 23, no. 4, pages 483–492, 1942.

Electrocardiograms represent the potential variations of a single electrode. American Heart Journal, vol. 9, no. 4, pages 447–458, 1934.

[13] Frank N Wilson, Franklin D Johnston, Francis F Rosenbaum, Herman Erlanger, Charles E Kossmann, Hans Hecht, Nelson Cotrim, Roberto Menezes de Oliveira, Roberto Scarsi and Paul S Barker. The precordial electrocardiogram. American Heart Journal, vol. 27, no. 1, pages 19–85, 1944.

#### Chapter I: Anatomy and functionality of the human heart

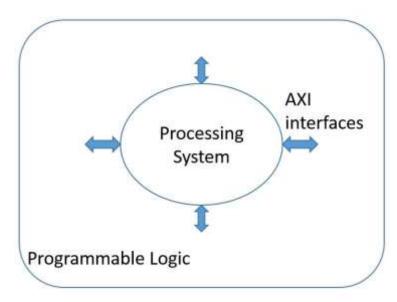

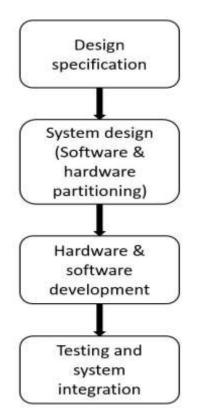

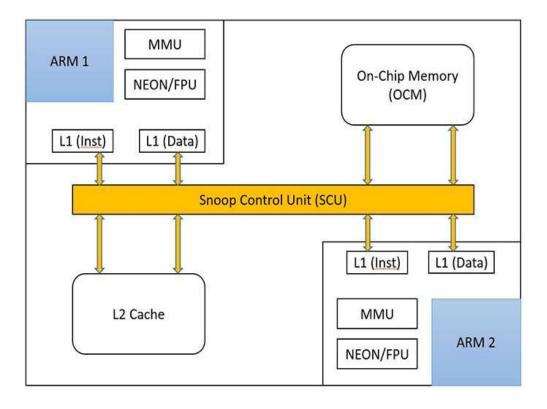

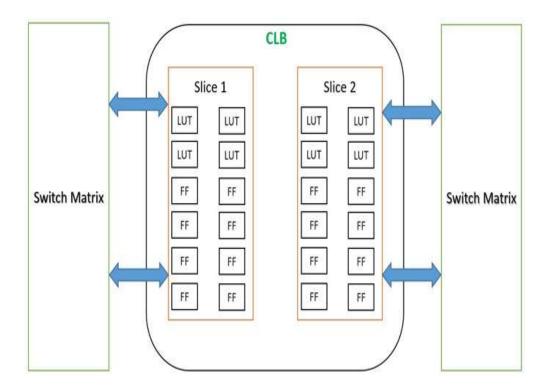

[14] Aljuaid M., Marashly Q., AlDanaf J., Tawhari I., Barakat M., Barakat R., Zobell B., Cho W., Chelu M.G., Marrouche N.F. Smartphone ECG monitoring system helps lower emergency room and clinic visits in post–atrial fibrillation ablation patients. *Clin. Med. Insights Cardiol.* 2020.