#### الجمهورية الجزائرية الديمقراطية الشعبية

République Algérienne Démocratique et Populaire Ministère de L'Enseignement Supérieur et de la Recherche Scientifique

# UNIVERSITÉ FERHAT ABBAS - SETIF1 FACULTÉ DE TECHNOLOGIE

### **THESE**

Présentée au Département d'électronique

Préparée au sein du Laboratoire d'instrumentation scientifique

( L.I.S )

Pour l'obtention du diplôme de

#### **DOCTORAT EN SCIENCES**

**Option: Electronique**

Par

#### **MERABET Mohammed**

## **THÈME**

## Test des Circuits Analogiques à Base de la Logique Floue par Voie de Simulation

#### Soutenue le 06/02/2020 devant le Jury:

| AMARDJIA Nouredine        | Professeur | Univ. Ferhat Abbas Sétif 1 | Président          |

|---------------------------|------------|----------------------------|--------------------|

| <b>BOUROUBA Nacerdine</b> | Professeur | Univ. Ferhat Abbas Sétif 1 | Directeur de thèse |

| <b>BOUZIT Nacerdine</b>   | Professeur | Univ. Ferhat Abbas Sétif 1 | Examinateur        |

| KHEDROUCHE Djamel         | Professeur | Univ. M. Boudiaf M'sila    | Examinateur        |

| AYAD Mouloud              | M.C.A      | Univ. A.M.O Bouira         | Examinateur        |

| AIT KAKI Abdelaziz        | M.C.A      | Univ. L.B.M. Oum bouaghi   | Examinateur        |

#### REMERCIEMENTS -

Je tiens tout d'abord à exprimer toute ma reconnaissance à mon encadreur Monsieur Nacerdine BOUROUBA, Professeur à l'université Ferhat Abbas Sétif 1, et responsable du groupe TCM au "Laboratoire d'instrumentation scientifique "(L.I.S), de m'avoir accueilli au sein de son équipe de recherche. Je lui exprime ma profonde gratitude pour ses conseils précieux, ses encouragements et son encadrement fructueux dont j'ai bénéficié. Ainsi pour ses qualités professionnelles et humaines que j'ai admirées et surtout pour la confiance qu'il a mise en moi pour accomplir ce travail.

Mes remerciements vont également à Monsieur AMARDJIA Nouredine, Professeur à l'Université Ferhat Abbas Sétif 1, de m'avoir fait l'honneur de présider le jury de cette thèse. Je remercie au même titre Monsieur Mouloud AYAD, Maitre de conférences classe A à l'université Akli Mohand Oulhadjde Bouira, Monsieur KHEDROUCHE Djamel, Professeur à l'Université Mohamed Boudiaf Msila, Monsieur BOUZIT Nacerdine, Professeur à l'Université Ferhat Abbas Sétif 1 et Monsieur AIT KAKI Abdelaziz, Maitre de conférences classe A à l'Université Larbi ben M'hidi Oum El-bouaghi, qui m'ont fait l'honneur d'accepter d'être examinateurs et membres du jury de ce mémoire de thèse, et d'avoir bien voulu me faire profiter de leurs remarques constructives, ainsi que pour les enrichissantes observations faites dans leurs rapports.

Enfin, je remercie toute l'équipe du TCM et notamment Mr. GAMOURA Amar, ARABI Abderezak, LAIDANI Imad, KOUACHI Sabah et BRAHIMI Abdelhalim, pour la bonne ambiance générale qu'ils ont su imposer au laboratoire et pour les longues et fructueuses discussions techniques que nous avons eues ensemble.

## Dédicace

Je dédie ce travail A mes parents,

A ma femme et mes enfants,

A mes frères et mes sœurs.

#### **RESUME -**

Avec le développement rapide de la microélectronique et de la technologie des semiconducteurs, les systèmes électroniques analogiques intégrés développent des fonctions plus sophistiquées et complexes et deviennent de plus en plus exigeants en termes de fiabilité. Par conséquent, la nécessité de disposer de méthodes automatiques pour leurs tests et leurs diagnostics représente un problème crucial aux chercheurs en la matière dans ce domaine. Le développement d'approches et de méthodes efficaces pour la détection et la classification des défauts dans les circuits analogiques constitue la pierre angulaire de tout projet de recherche relatif à la conception de test visant à améliorer la performance des circuits intégrés.

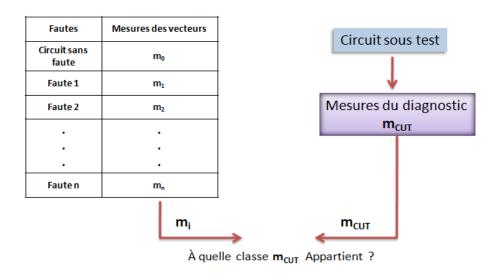

Cette thèse permis d'introduire l'utilisation des techniques de la logique floue pour la détection et la localisation de défauts catastrophiques dans des circuits électroniques analogiques comprenant des transistors bipolaires. Pour ce faire, des simulations du circuit sous test (CUT) sont effectuées pour un examen de la réponse du circuit testé dans des conditions défectueuses et sans défaut. A cette fin, deux paramètres de signature - tension de sortie et courant d'alimentation - sont observés en mode DC, et utilisés pour construire un dictionnaire de fautes. Celui ci est utilisé efficacement pour produire un système d'inférence floue (FIS) capable de réorganiser les données structurées numériquement et de les exploiter pour améliorer la précision de la localisation et l'identification des défauts. Finalement, les résultats obtenus des différentes expériences sont présentés pour justifier l'applicabilité de la méthode proposée et confirment sa validité.

*Mots clés*: Test, détection de fautes, localisation de fautes, Circuits analogiques, Logique floue, Système d'inférence floue.

### ABSTRACT -

With the fast progress of microelectronics and semiconductor technology, integrated analog electronic systems are growing in more sophisticated and complex functions and become very needy of a high reliability. Therefore, the automatic methods requirement for their tests and diagnostic is a crucial issue for researchers in this field. The development of effective approaches and techniques for detection and classification of defects in analogue circuits is the cornerstone of any test design research project aimed at improving the performance of integrated circuits.

This thesis introduces the fuzzy logic techniques use—for hard faults detection and location in analog electronic circuits built with bipolar transistors. For this purpose, primary, simulations of the circuit under test (CUT) are performed before the test stage by investigating the response of the circuit under test in faulty and fault-free conditions. Afterward, two signatures parameters—the output voltage and the supply current—are observed in DC domain simulation and used to build a fault dictionary. This is used effectively to produce a fuzzy inference system (FIS) which is able to reorganizing structured data digitally and uses them to improve—fault location and identification more accurately Finally, the results of different experiments are presented to demonstrate the applicability of the proposed method by increasing its efficiency.

*Keywords:* Test, Fault detection, Fault localization, Analog circuits, Fuzzy logic, Fuzzy inference system.

## **Sommaire**

| -      | •         |            |

|--------|-----------|------------|

| Unn    | nerciem   | anta       |

| $\sim$ | iei Cieii | IC I I I S |

|        |           |            |

Résumé

Liste des Figures

Liste des Tableaux

Liste des abréviations

Introduction générale

## Chapitre 1 : Concepts de base test des circuits et systèmes intégrés

| 1.1. Introduction                                       | l  |

|---------------------------------------------------------|----|

| 1.2. Notions de base du test                            | 3  |

| 1.2.1. Défauts                                          | 4  |

| 1.2.2. Fautes                                           | 5  |

| 1.2.3. Erreurs                                          | 5  |

| 1.3. Le test dans le cycle de vie des circuits intégrés | 6  |

| 1.3.1. Le test de caractérisation.                      | 6  |

| 1.3.2. Le test de production.                           | 7  |

| 1.4. Les défauts dans les circuits intégrés             | 8  |

| 1.4.1. Sources des fautes                               | 9  |

| 1.4.2. Classification des fautes                        | 9  |

| 1.4.2.1. Les fautes catastrophiques                     | 11 |

| 1.4.2.2. Les fautes paramétriques                       | 12 |

| 1.5. Classement de test                                 | 12 |

| 1.5.1. Aspect technologique                             | 12 |

| 1.5.1.1. Les circuits analogiques                       | 12 |

| 1.5.1.2. Les circuits numériques                        | 13 |

| 1.5.1.3. Les circuits mixtes                            | 13 |

| 1.5.2. Aspect des paramètres mesurés                    | 13 |

| 1.5.2.1. Tests logiques                                 | 13 |

| 1.5.2.2. Tests électriques                              | 13 |

| 1.5.3. L'utilisation des résultats du test              | 14 |

| 1.5.4. Méthode d'application du test                    | 15 |

|                                                         |    |

| 1.6. Types de test                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.6.1. Test fonctionnel                                                                                                                                                                                                                                                             |

| 1.6.2. Test structurel                                                                                                                                                                                                                                                              |

| 1.6.3. Test alternatif                                                                                                                                                                                                                                                              |

| 1.7. Conception en vue du test                                                                                                                                                                                                                                                      |

| 1.7.1. Les techniques Ad-hoc                                                                                                                                                                                                                                                        |

| 1.7.2. Les techniques de scan (SCAN-PATH)19                                                                                                                                                                                                                                         |

| 1.7.3. L'auto-test (BIST : Built In Self Test)                                                                                                                                                                                                                                      |

| 1.7.4. Le test des frontières (IEEE 1149.1 Boundary Scan Standard)                                                                                                                                                                                                                  |

| 1.8. coût de test d'un circuit                                                                                                                                                                                                                                                      |

| 1.9. Conclusion                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                     |

| Chapitre 2 : Diagnostic de fautes des circuits analogiques                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                     |

| 2.1. Introduction                                                                                                                                                                                                                                                                   |

| 2.2. Test et diagnostic                                                                                                                                                                                                                                                             |

| 2.3. Complexité du test et du diagnostic des circuits analogiques24                                                                                                                                                                                                                 |

| 2.4. Tâches des systèmes de diagnostic des fautes                                                                                                                                                                                                                                   |

| 2.5. Modélisation des fautes analogiques                                                                                                                                                                                                                                            |

| 2.5.1. Modélisation structurelle (au niveau composant)                                                                                                                                                                                                                              |

| 2.5.2. Modélisation paramétrique                                                                                                                                                                                                                                                    |

| 2.5.3. Modélisation au niveau fonctionnel (comportemental)29                                                                                                                                                                                                                        |

| 2.6. Simulation de fautes et génération des vecteurs de test                                                                                                                                                                                                                        |

| 2.6.1. Simulation de fautes                                                                                                                                                                                                                                                         |

| 2.0.1. Simulation de nates                                                                                                                                                                                                                                                          |

| 2.6.2. Génération de vecteurs de test                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                     |

| 2.6.2. Génération de vecteurs de test                                                                                                                                                                                                                                               |

| 2.6.2. Génération de vecteurs de test                                                                                                                                                                                                                                               |

| 2.6.2. Génération de vecteurs de test                                                                                                                                                                                                                                               |

| 2.6.2. Génération de vecteurs de test302.7. Techniques employées pour le diagnostic de fautes des circuits analogiques312.7.1. Simulation avant test (SBT)332.7.1.1. Approche basée sur des règles34                                                                                |

| 2.6.2. Génération de vecteurs de test302.7. Techniques employées pour le diagnostic de fautes des circuits analogiques312.7.1. Simulation avant test (SBT)332.7.1.1. Approche basée sur des règles342.7.1.2. Méthode de dictionnaire de fautes35                                    |

| 2.6.2. Génération de vecteurs de test302.7. Techniques employées pour le diagnostic de fautes des circuits analogiques312.7.1. Simulation avant test (SBT)332.7.1.1. Approche basée sur des règles342.7.1.2. Méthode de dictionnaire de fautes352.7.2. Simulation après test(SAT)36 |

| 2.8. Approches de Localisation et de Classification de fautes            |

|--------------------------------------------------------------------------|

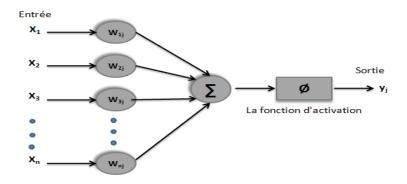

| 2.8.1. Les réseaux de neurones artificiels (ANN)                         |

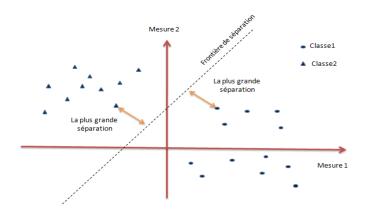

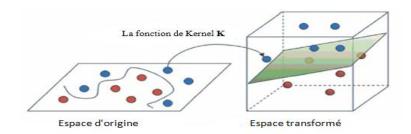

| 2.8.2. Machine à vecteurs de support (SVM : Support Vector Machine)40    |

| 2.8.3. La logique floue                                                  |

| 2.9. Conclusion                                                          |

| Chapitre 3 : La logique floue                                            |

| 3.1. Introduction                                                        |

| 3.2. Historique                                                          |

| 3.3. Principes de la logique floue                                       |

| 3.4. Les concepts principaux de la logique floue                         |

| 3.4.1. Les ensembles flous                                               |

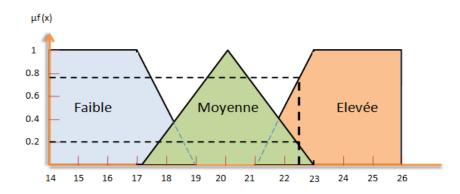

| 3.4.2. Fonctions d'appartenances                                         |

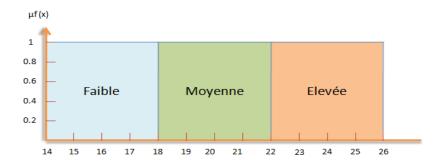

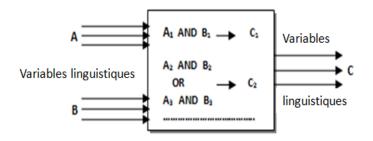

| 3.4.3. Variable linguistique51                                           |

| 3.4.4. Opérateurs flous                                                  |

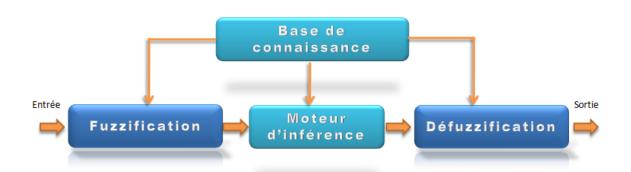

| 3.5. Système d'inférence flou                                            |

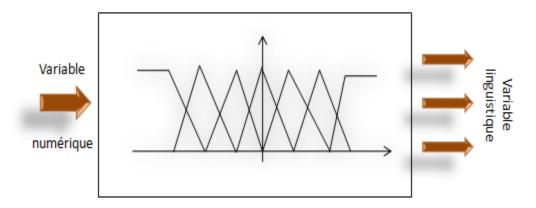

| 3.5.1. Fuzzification                                                     |

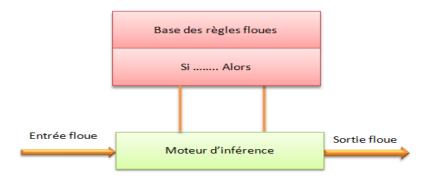

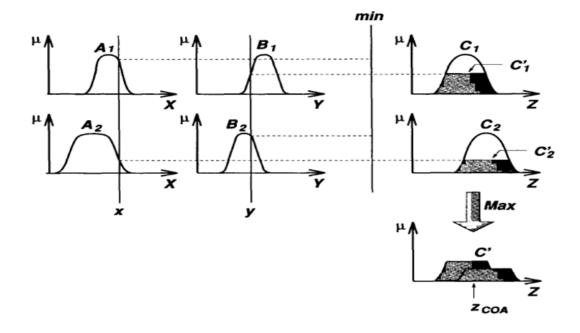

| 3.5.2. Module d'inférences                                               |

| 3.5.3. Défuzzification                                                   |

| 3.6. Conclusion                                                          |

| Chapitre 4 : Le Test en mode DC pour la détection de fautes des circuits |

| Analogiques                                                              |

| 4.1. Introduction                                                        |

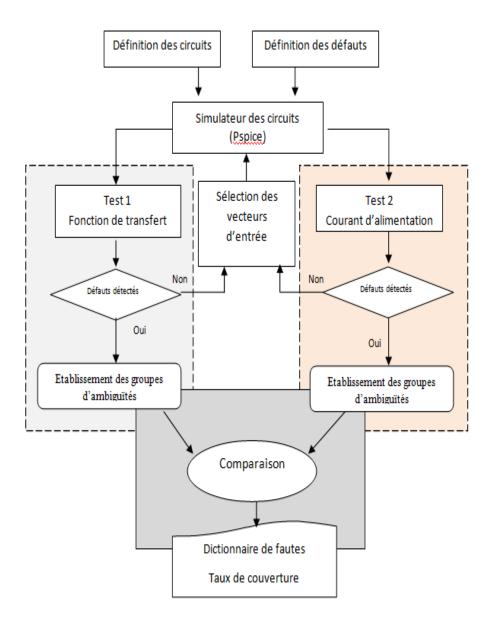

| 4.2. Méthodologie proposée                                               |

| 4.3. Concept d'ambiguïté                                                 |

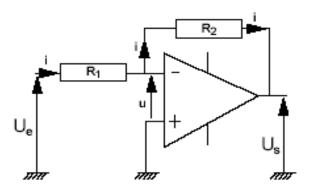

| 4.4. Exemple 1 : L'amplificateur inverseur à base de μA 74166            |

| 4.4.1. Structure des transistors utilisés                                |

| 4.4.2. Le mode et le vecteur de test choisis                             |

| 4.4.3. Les défauts employés                                              |

| 4.4.4. Procédure de test basée sur la fonction de transfert              |

| 4.4.4.1. Critère de détection                                                   |

|---------------------------------------------------------------------------------|

| 4.4.4.2. Couverture de fautes et formation de groupes d'ambigüité74             |

| 4.4.5. Maximalisation de la détection de fautes par le test basé sur le courant |

| d'alimentation76                                                                |

| 4.4.5.1. Couverture de fautes et formation de groupes d'ambigüité79             |

| 4.4.5.2. Comparaison des résultats de deux tests                                |

| 4.5. Exemple 2 : Le régulateur de tension80                                     |

| 4.5.1. Test par fonction de transfert82                                         |

| 4.5.2. Test par courant d'alimentation85                                        |

| 4.5.3. Comparaison                                                              |

| 4.6. Conclusion                                                                 |

|                                                                                 |

| Chapitre 5 : Identification et Localisation des fautes en utilisant les         |

| techniques de la logique floue                                                  |

|                                                                                 |

| 5.1. Introduction                                                               |

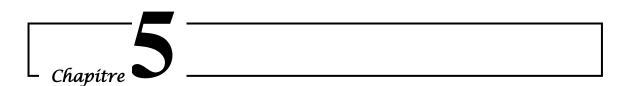

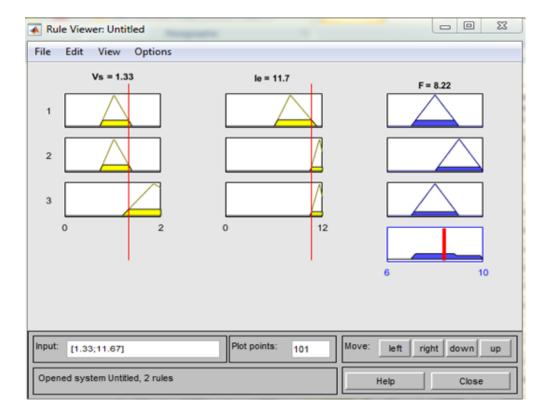

| 5.2. Module d'inférence floue du logiciel Matlab92                              |

| 5.3. La conception du système d'inférence floue                                 |

| 5.4. Application de la localisation des fautes à l'amplificateur inverseur96    |

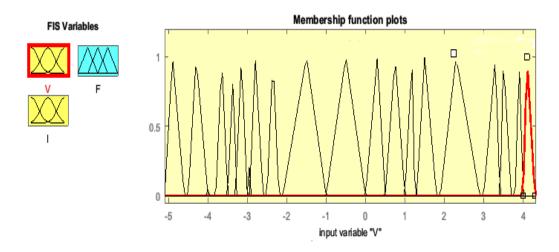

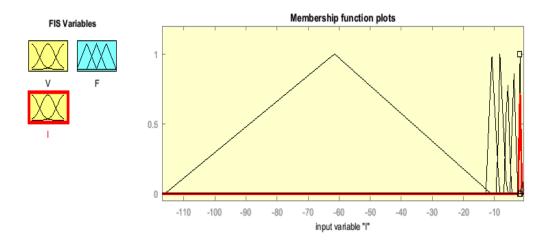

| 5.4.1. Fuzzification                                                            |

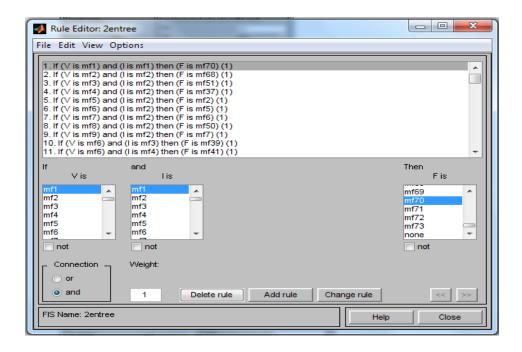

| 5.4.2. Les règles d'inférence                                                   |

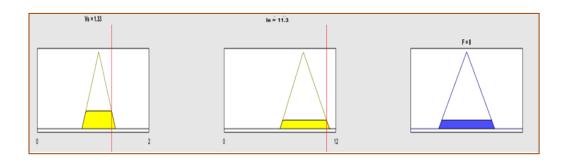

| 5.4.3. Défuzzification                                                          |

| 5.4.4. Exemples explicatifs et résultats                                        |

| 5.5. Localisation de fautes pour le régulateur de tension                       |

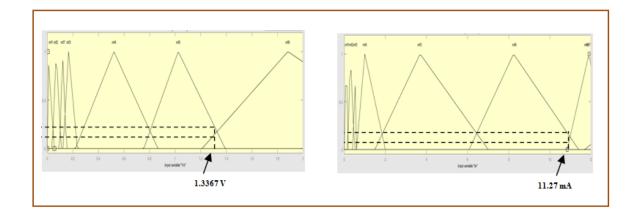

| 5.5.1. Fuzzification                                                            |

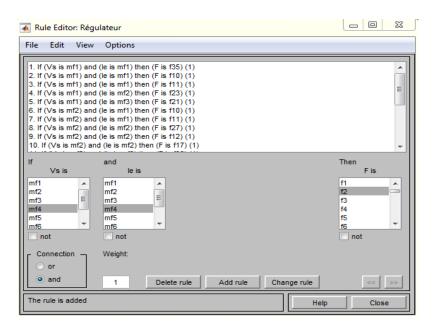

| 5.5.2. Édition des règles floues                                                |

| 5.5.3. Exemple récapitulatif et résultats                                       |

| 5.6. Conclusion                                                                 |

|                                                                                 |

| Conclusion et perspectives                                                      |

| Bibliographie                                                                   |

| Productions scientifiques                                                       |

## Liste des Figures

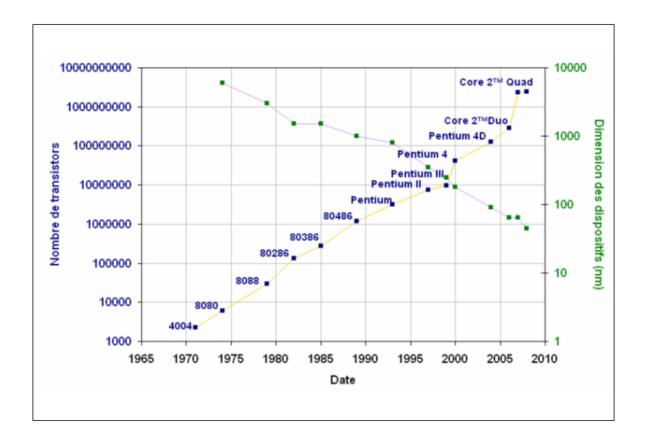

| Figure 1.1. Représentation de la loi de Moore avec l'exemple des $\mu P$ d'Intel      | .3       |

|---------------------------------------------------------------------------------------|----------|

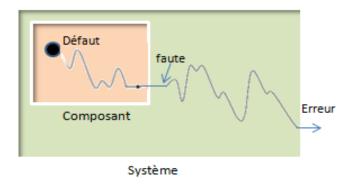

| Figure 1.2. Différents niveaux d'abstraction du défaut                                | .5       |

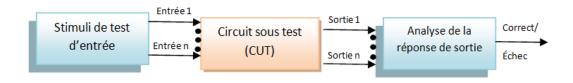

| Figure 1.3. Approche de base du test                                                  | 6        |

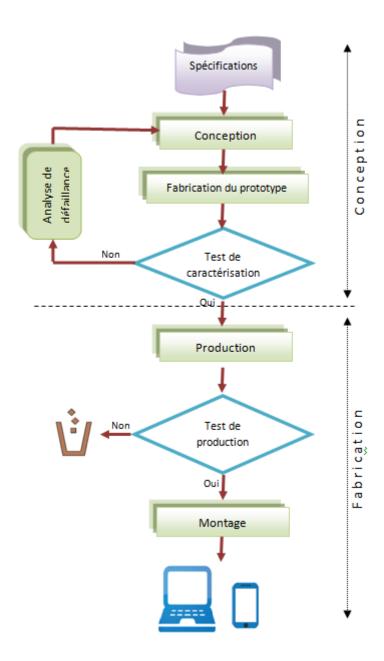

| Figure 1.4. Cycle de conception et de fabrication des circuits intégrés               | .7       |

| Figure 1.5. Classification des fautes                                                 | l 1      |

| Figure 1.6. Principe d'un test fonctionnel.                                           | 6        |

| Figure 1.7. Principe d'un test structurel.                                            | 7        |

| <b>Figure 1.8.</b> Correspondance entre mesures de test et performances               | 8        |

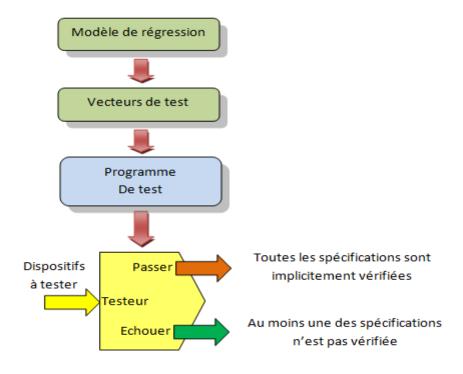

| Figure 1.9. Principe de test alternatif                                               | 8        |

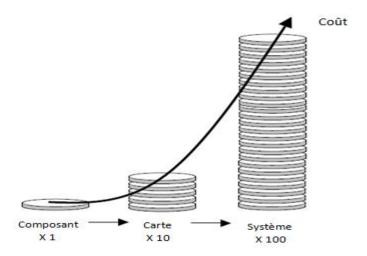

| <b>Figure 1.10.</b> Coûts de détection des défauts (règle de (×10))                   | )        |

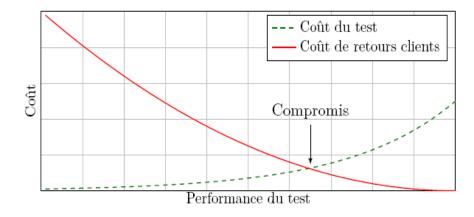

| Figure 1.11. Illustration qualitative du compromis entre le coût du test et le coût d | es       |

| retours clients (d'après l'ITRS)                                                      | 21       |

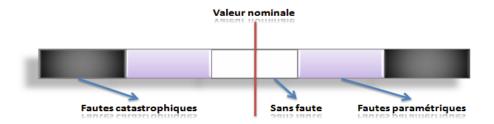

| <b>Figure 2.1.</b> Bandes de tolérance pour les différents types de fautes            | 7        |

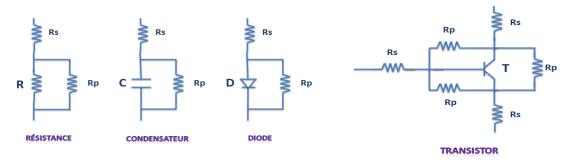

| Figure 2.2. modèles de fautes.                                                        | 27       |

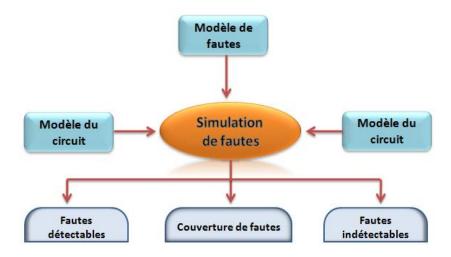

| <b>Figure 2.3.</b> Méthodologie de la simulation de fautes                            | 0        |

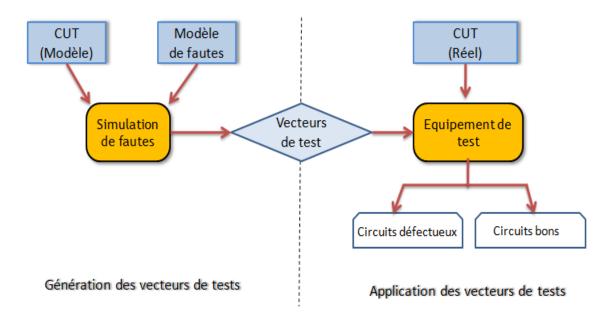

| Figure 2.4. Génération et application des vecteurs de test                            | 31       |

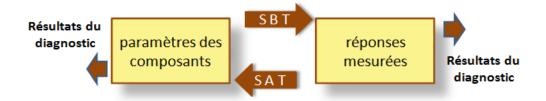

| Figure 2.5. Description des approches SBT et SAT.                                     | 33       |

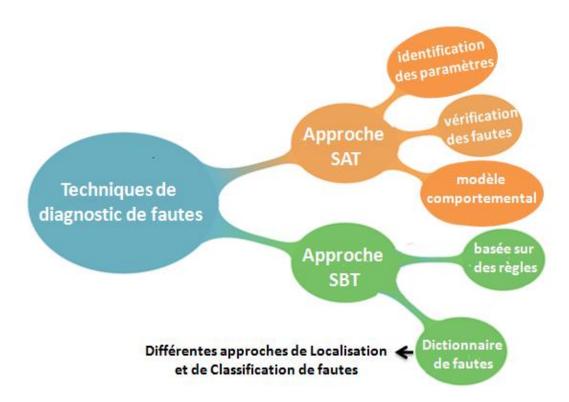

| Figure 2.6. Classification des différentes approches de diagnostic des fautes         | 33       |

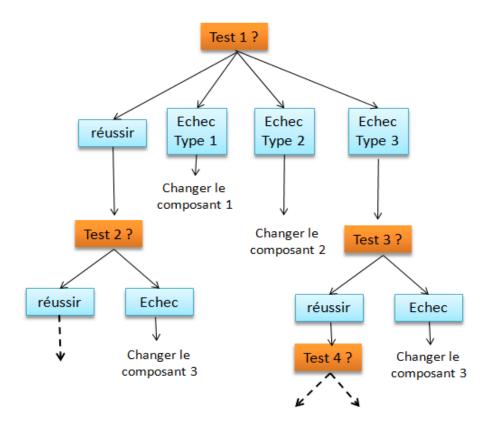

| <b>Figure 2.7.</b> Arbre de défaillance simple                                        | 4        |

| <b>Figure 2.8.</b> Méthode de dictionnaire de fautes                                  | 6        |

| <b>Figure 2.9.</b> Un ANN monocouche                                                  | 0        |

| <b>Figure 2.10.</b> Hyperplan à marge maximale utilisé dans SVM                       | .1       |

| <b>Figure 2.11 .</b> Mappage spatial du SVM à l'aide de la fonction kernel4           | 1        |

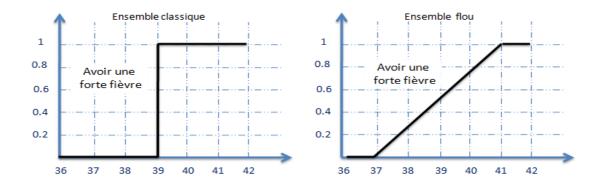

| <b>Figure 3.1.</b> Logique classique et logique floue                                 | 5        |

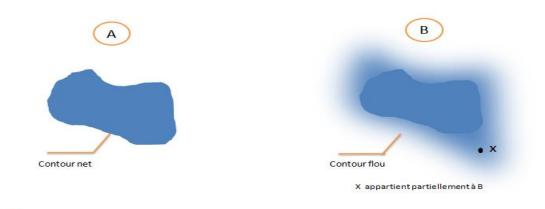

| <b>Figure 3.2.</b> Représentation d'un ensemble classique et d'un ensemble flou       | 7        |

| Figure 3.3. Appartenance de la température en logique classique et la logique floue48 | <b>,</b> |

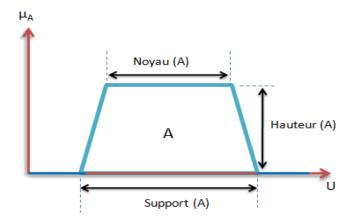

| Figure 3.4. Caractéristiques d'un sous ensemble flou                                  | )        |

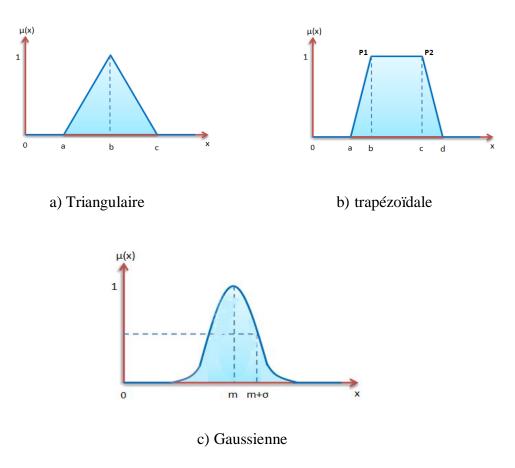

| <b>Figure 3.5.</b> Formes usuelles des fonctions d'appartenance                       | -        |

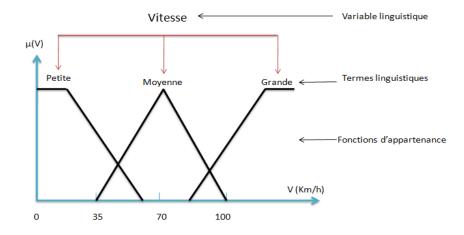

| Figure 3.6 Variable linguistique                                                      | 2        |

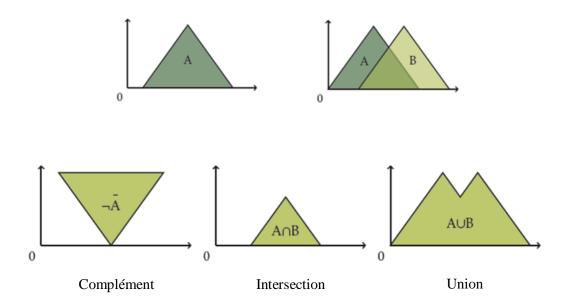

| <b>Figure 3.7.</b> Opérateurs flous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Figure 3.8.</b> Architecture de base d'un système d'inférence floue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <b>Figure 3.9.</b> Module d'inférence d'un système flou                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <b>Figure 3.10.</b> Processus d'inférence floue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <b>Figure 3.11.</b> Composition Max-min de Mamdani                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

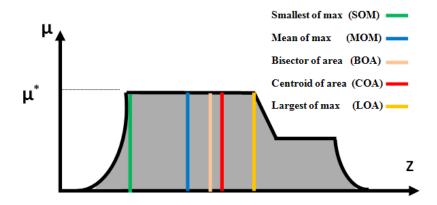

| <b>Figure 3.12.</b> Différentes méthodes de défuzzification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <b>Figure 4.1.</b> Méthodologie de détection de fautes proposée                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

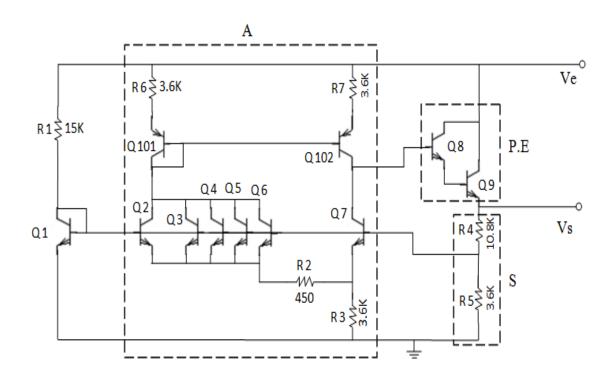

| <b>Figure 4.2.</b> Amplificateur inverseur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

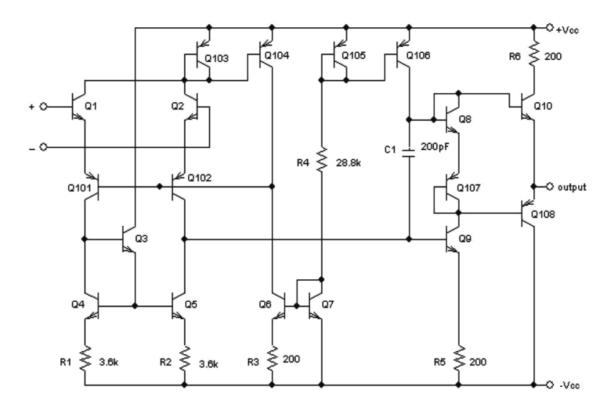

| <b>Figure 4.3.</b> Amplificateur opérationnel uA741                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

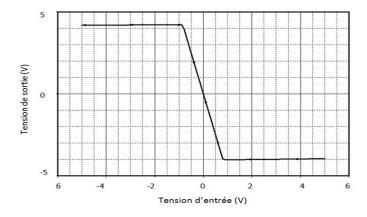

| <b>Figure 4.4.</b> Structure des transistors utilisés                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

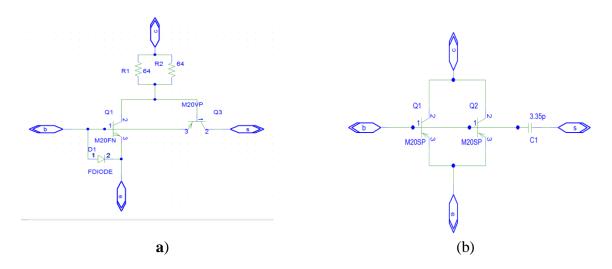

| <b>Figure 4.5.</b> Court circuit et circuit ouvert                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <b>Figure 4.6.</b> Faute double71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

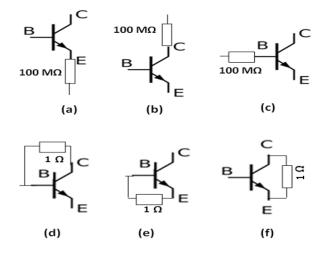

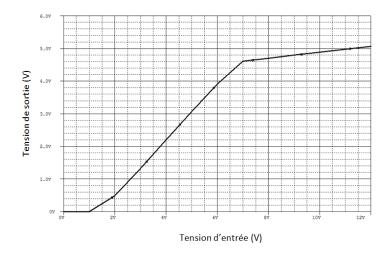

| <b>Figure 4.7.</b> Fonction de transfert de l'amplificateur inverseur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

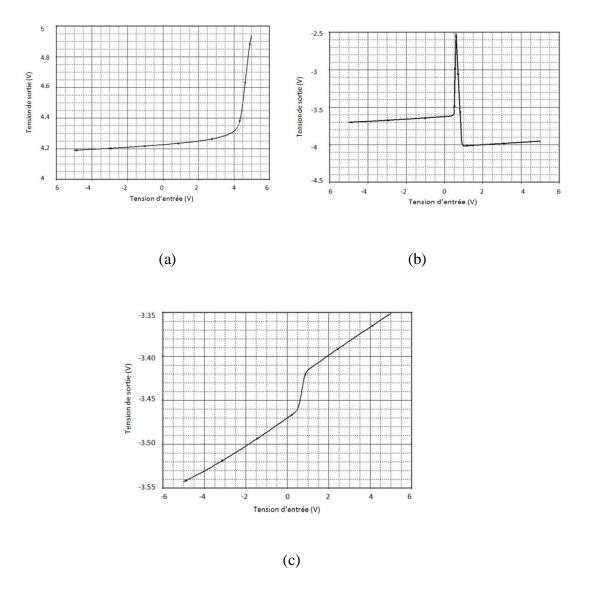

| Figure 4.8. Fonction de transfert de l'amplificateur inverseur sous différentes fautes72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

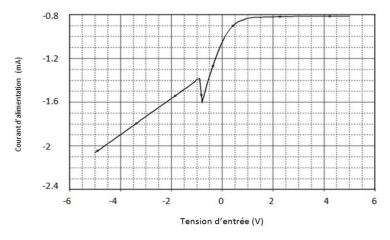

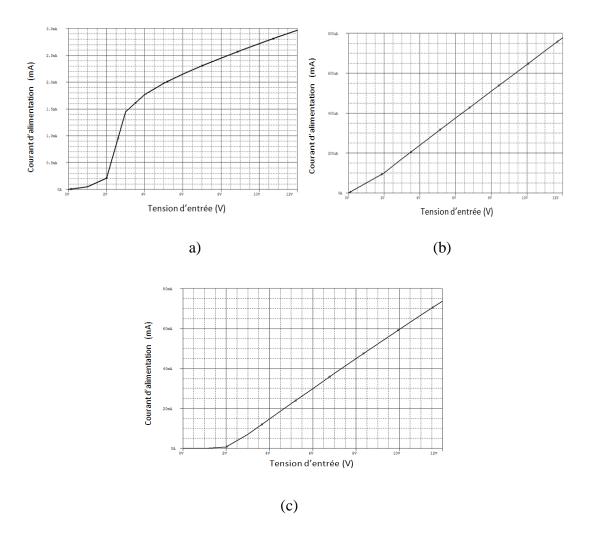

| Figure 4.9. Caractéristique Ie=f(Ve) de l'amplificateur inverseur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

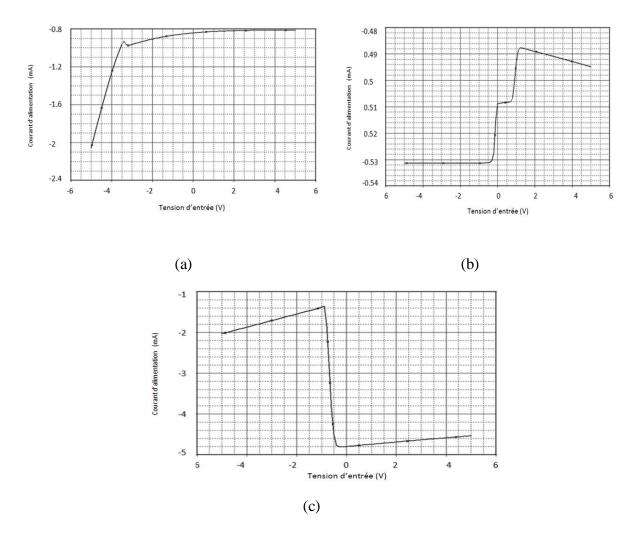

| Figure 4.10. Caractéristique de l'amplificateur inverseur sous différentes fautes77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 4.11 Déculatour de tension positive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 4.11. Régulateur de tension positive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 4.11. Regulateur de tension positive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

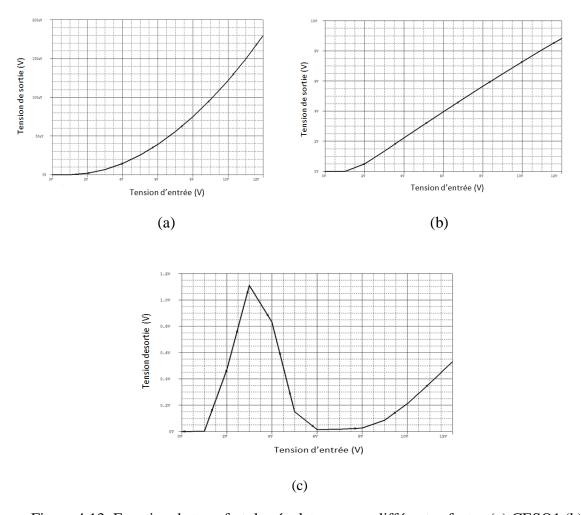

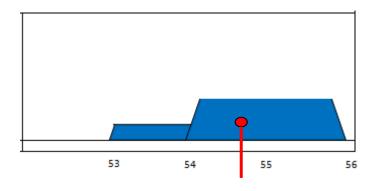

| <b>Figure 4.12.</b> Fonction de transfert du régulateur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 4.12. Fonction de transfert du régulateur       82         Figure 4.13. Fonction de transfert du régulateur sous différentes fautes       83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 4.12. Fonction de transfert du régulateur82Figure 4.13. Fonction de transfert du régulateur sous différentes fautes83Figure 4.14. Caractéristique Ie=f(Ve) du régulateur de tension85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 4.12. Fonction de transfert du régulateur82Figure 4.13. Fonction de transfert du régulateur sous différentes fautes83Figure 4.14. Caractéristique Ie=f(Ve) du régulateur de tension85Figure 4.15. Caractéristique Ie=f(Ve) du régulateur sous différentes fautes86                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

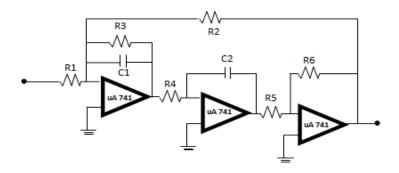

| Figure 4.12. Fonction de transfert du régulateur82Figure 4.13. Fonction de transfert du régulateur sous différentes fautes83Figure 4.14. Caractéristique Ie=f(Ve) du régulateur de tension85Figure 4.15. Caractéristique Ie=f(Ve) du régulateur sous différentes fautes86Figure 4.16. Filtre passe-bas de deuxième ordre89                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 4.12. Fonction de transfert du régulateur82Figure 4.13. Fonction de transfert du régulateur sous différentes fautes83Figure 4.14. Caractéristique Ie=f(Ve) du régulateur de tension85Figure 4.15. Caractéristique Ie=f(Ve) du régulateur sous différentes fautes86Figure 4.16. Filtre passe-bas de deuxième ordre89Figure 5.1. Outils de la boîte à outils Fuzzy de Matlab93                                                                                                                                                                                                                                                                                                                                                           |

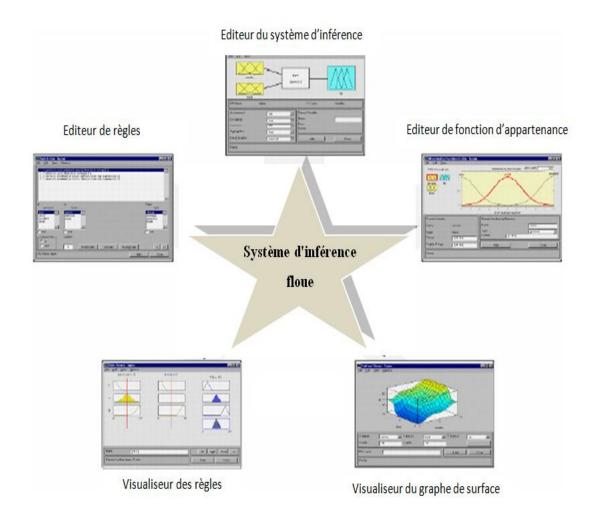

| Figure 4.12. Fonction de transfert du régulateur82Figure 4.13. Fonction de transfert du régulateur sous différentes fautes83Figure 4.14. Caractéristique Ie=f(Ve) du régulateur de tension85Figure 4.15. Caractéristique Ie=f(Ve) du régulateur sous différentes fautes86Figure 4.16. Filtre passe-bas de deuxième ordre89Figure 5.1. Outils de la boîte à outils Fuzzy de Matlab93Figure 5.2. Aperçu général du système flou proposé94                                                                                                                                                                                                                                                                                                       |

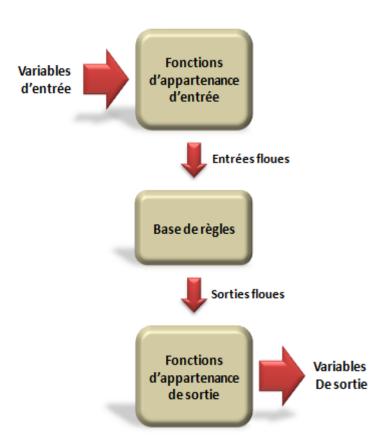

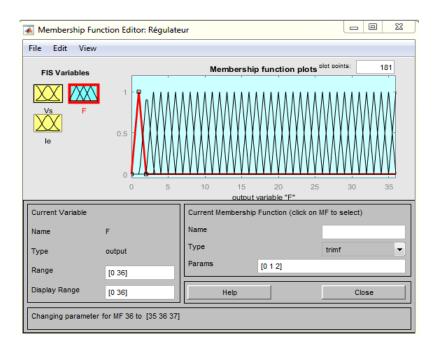

| Figure 4.12. Fonction de transfert du régulateur82Figure 4.13. Fonction de transfert du régulateur sous différentes fautes83Figure 4.14. Caractéristique Ie=f(Ve) du régulateur de tension85Figure 4.15. Caractéristique Ie=f(Ve) du régulateur sous différentes fautes86Figure 4.16. Filtre passe-bas de deuxième ordre89Figure 5.1. Outils de la boîte à outils Fuzzy de Matlab93Figure 5.2. Aperçu général du système flou proposé94Figure 5.3. Fenêtre principale de l'éditeur de logique floue95                                                                                                                                                                                                                                         |

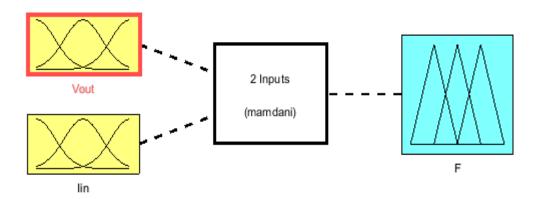

| Figure 4.12. Fonction de transfert du régulateur82Figure 4.13. Fonction de transfert du régulateur sous différentes fautes83Figure 4.14. Caractéristique Ie=f(Ve) du régulateur de tension85Figure 4.15. Caractéristique Ie=f(Ve) du régulateur sous différentes fautes86Figure 4.16. Filtre passe-bas de deuxième ordre89Figure 5.1. Outils de la boîte à outils Fuzzy de Matlab93Figure 5.2. Aperçu général du système flou proposé94Figure 5.3. Fenêtre principale de l'éditeur de logique floue95Figure 5.4. Système d'inférence floue « Mamdani » (deux entrées)96                                                                                                                                                                       |

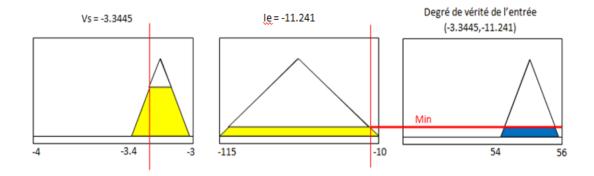

| Figure 4.12. Fonction de transfert du régulateur82Figure 4.13. Fonction de transfert du régulateur sous différentes fautes83Figure 4.14. Caractéristique Ie=f(Ve) du régulateur de tension85Figure 4.15. Caractéristique Ie=f(Ve) du régulateur sous différentes fautes86Figure 4.16. Filtre passe-bas de deuxième ordre89Figure 5.1. Outils de la boîte à outils Fuzzy de Matlab93Figure 5.2. Aperçu général du système flou proposé94Figure 5.3. Fenêtre principale de l'éditeur de logique floue95Figure 5.4. Système d'inférence floue « Mamdani » (deux entrées)96Figure 5.5. Processus de fuzzification97                                                                                                                               |

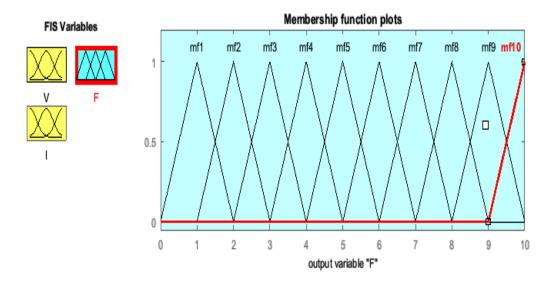

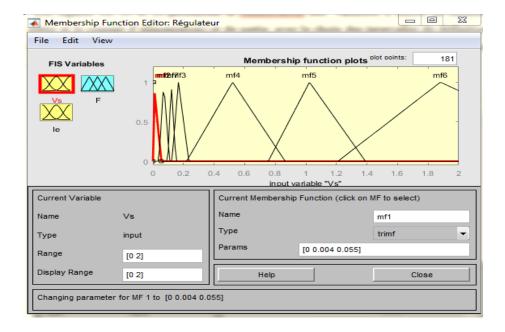

| Figure 4.12. Fonction de transfert du régulateur82Figure 4.13. Fonction de transfert du régulateur sous différentes fautes83Figure 4.14. Caractéristique Ie=f(Ve) du régulateur de tension85Figure 4.15. Caractéristique Ie=f(Ve) du régulateur sous différentes fautes86Figure 4.16. Filtre passe-bas de deuxième ordre89Figure 5.1. Outils de la boîte à outils Fuzzy de Matlab93Figure 5.2. Aperçu général du système flou proposé94Figure 5.3. Fenêtre principale de l'éditeur de logique floue95Figure 5.4. Système d'inférence floue « Mamdani » (deux entrées)96Figure 5.5. Processus de fuzzification97Figure 5.6. Fonctions d'appartenance de la tension de sortie98                                                                 |

| Figure 4.12. Fonction de transfert du régulateur82Figure 4.13. Fonction de transfert du régulateur sous différentes fautes83Figure 4.14. Caractéristique Ie=f(Ve) du régulateur de tension85Figure 4.15. Caractéristique Ie=f(Ve) du régulateur sous différentes fautes86Figure 4.16. Filtre passe-bas de deuxième ordre89Figure 5.1. Outils de la boîte à outils Fuzzy de Matlab93Figure 5.2. Aperçu général du système flou proposé94Figure 5.3. Fenêtre principale de l'éditeur de logique floue95Figure 5.4. Système d'inférence floue « Mamdani » (deux entrées)96Figure 5.5. Processus de fuzzification97Figure 5.6. Fonctions d'appartenance de la tension de sortie98Figure 5.7. Fonctions d'appartenance du courant d'alimentation98 |

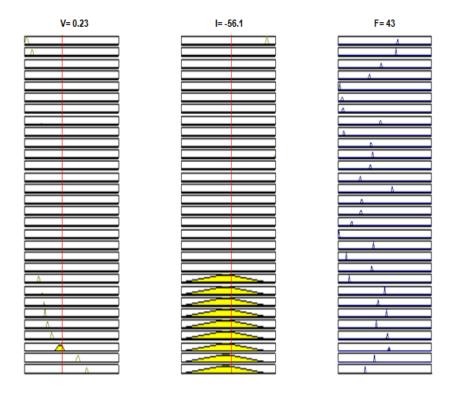

| Figure 5.11. Agrégation floue                                                 | 101 |

|-------------------------------------------------------------------------------|-----|

| Figure 5.12. Défuzzification avec la méthode centre de gravité                | 102 |

| Figure 5.13. La sortie du FIS pour la faute F43                               | 103 |

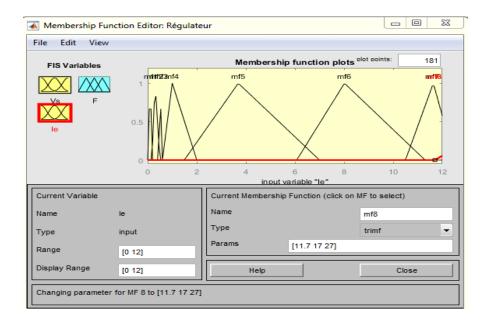

| Figure 5.14. Fonctions d'appartenance de la tension de sortie du régulateur   | 108 |

| Figure 5.15. Fonctions d'appartenance du courant d'alimentation du régulateur | 108 |

| Figure 5.16. Fonctions d'appartenance de sortie                               | 109 |

| Figure 5.17. Les règles floues pour le régulateur de tension                  | 110 |

| Figure 5.18. Exemple de fuzzification                                         | 110 |

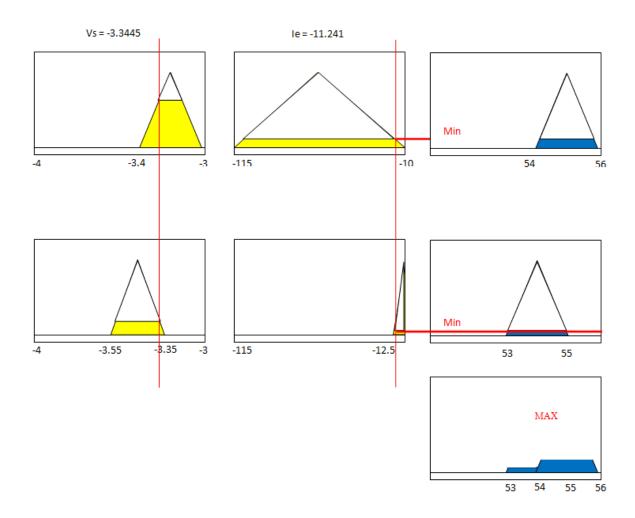

| Figure 5.19. La conclusion de l'implication de la règle 1                     | 111 |

| Figure 5.20. L'ensemble flou des règles 1,2 et 3                              | 112 |

## Liste des Tableaux

| Tableau 1.1: Principaux mécanismes de défaillances et défauts pouvant altérer le bon          |

|-----------------------------------------------------------------------------------------------|

| fonctionnement d'un circuit intégré10                                                         |

| Tableau 4.1. Les tensions des nœuds d'un circuit hypothétique sans défaut et pour diverses    |

| conditions défectueuses64                                                                     |

| Tableau 4.2. Groupes d'ambiguïtés et plages de tension                                        |

| Tableau 4.3. Paramètres des modèles des composants (a) Diode zener (b) Transistors68          |

| Tableau 4.4. Dictionnaire de fautes pour la fonction de transfert                             |

| <b>Tableau 4.5.</b> Formation de groupes d'ambigüité.    75                                   |

| Tableau 4.6. Dictionnaire de fautes pour le courant d'alimentation                            |

| Tableau 4.7. Formation de groupes d'ambigüité pour le test 2                                  |

| Tableau 4.8. Comparaison des résultats de deux tests                                          |

| Tableau 4.9. Dictionnaire de fautes pour la fonction de transfert du régulateur84             |

| Tableau 4.10. Groupes d'ambigüité résultant du test par fonction de transfert85               |

| Tableau 4.11. Dictionnaire de fautes pour le courant d'alimentation du régulateur87           |

| Tableau 4.12. Groupes d'ambigüité pour le test par courant d'alimentation                     |

| Tableau 4.13. Fautes localisés pour les deux modes de test.    88                             |

| <b>Tableau 5.1.</b> Les entrées et les sorties du FIS pour les cas de test F4, F49, et F52104 |

| Tableau 5.2. Les sorties Fis et leurs fautes correspondantes.    107                          |

| Tableau 5.3. Les sorties FIS et leurs fautes correspondantes pour le régulateur               |

## Liste des Abréviations

| Abréviations | Description                 |

|--------------|-----------------------------|

| AC           | Alternating Current         |

| ADC          | Analog to Digital Converter |

| ANN          | Artificial Neural Network   |

| ATE          | Automatic Test Equipment    |

| BCS          | Base Collector Short        |

| BES          | Base Emitter Short          |

| BIST         | Built-In Self-Test          |

| ВО           | Base Open                   |

| CC           | Court-Circuit               |

| CES          | CollectorEmitter Short      |

| CI           | Circuit Intégré             |

| СО           | Circuit Ouvert              |

| СО           | Collector Open              |

| CUT          | Circuit Under Test          |

| DAC          | Digital to Analog Converter |

| DC           | Direct Current              |

| DFT          | Design For Testability      |

| ЕО           | Emitter Open                |

| FIS          | Fuzzy Inference System      |

| IA           | Intelligence Artificielle   |

| ICT          | In Circuit Testing          |

| ITRS | International Roadmap for Semiconductors          |

|------|---------------------------------------------------|

| MOS  | Metal Oxyde Semiconductor                         |

| PCB  | Printed Circuit Boards                            |

| SAT  | Simulation After Test                             |

| SBT  | Simulation Before Test                            |

| SVM  | Support Vector Machine                            |

| TMF  | Triangular Membership Function                    |

| VHDL | Very-high-speed integrated circuits Hardware      |

| VLSI | Description Language Very Large Scale Integration |

#### INTRODUCTION GENERALE

Ces derniers temps, et grâce à l'essor technologique extraordinaire caractérisé par l'émergence de la nanoélectronique, il y a eu une véritable métamorphose dans le monde de la science et de la connaissance. Plusieurs nouveaux domaines sont devenus très importants dans la vie quotidienne et occupent une place importante dans la société actuelle, tels que la télécommunication, le multimédia, les applications biomédicales, etc. Ces domaines de la science sont devenus vivement sollicités par la communauté industrielle et des institutions de la recherche scientifique. Ils doivent leur mérite à l'insertion florissante des systèmes électroniques complexes aussi bien dans leur structure que dans leur fonctionnalité dont les composants clefs de ces systèmes électroniques sont les circuits intégrés [2] [5].

La tendance à l'évolution de la technologie des circuits intégrés à très grande échelle (VLSI), alimentée par une concurrence industrielle féroce pour réduire les coûts et les délais de mise sur le marché des circuits intégrés, a conduit à concevoir et fabriquer des circuits intégrés très complexes comprenant des pièces numériques, analogiques et mixtes dans une même puce de semi-conducteur. En raison de cette complexité croissante, la

conception et les tests sont devenus un véritable défi pour assurer la fonctionnalité et la qualité du produit [6] [7].

Le test des circuits et systèmes électroniques numériques a fait l'objet de recherches approfondies et des outils de diagnostic entièrement automatisés ont été mis au point avec succès. Cependant, le processus de développement de stratégies de test pour les circuits analogiques repose encore largement sur l'expérience et l'intuition de l'ingénieur [9].

La communauté de l'ingénierie a commencé à étudier les problèmes des tests analogiques au début des années 1980 [10], car les systèmes analogiques étaient parmi les systèmes les moins fiables et les moins testables. Depuis lors, le diagnostic analogique des défauts est devenu un domaine de recherche actif et de nombreuses méthodes ont été proposées dans la littérature [9].

Le diagnostic des circuits analogiques est devenu vital par l'ampleur de la gravité des problèmes de production des circuits intégrés et par conséquent il joue un rôle clé dans la conception des circuits électroniques [11] [46]. Contrairement aux circuits numériques, la méthodologie de diagnostic des défauts et de test des circuits analogiques reste relativement peu développée en raison de nombreuses limitations, par exemple les variations technologiques des paramètres dans leurs plages de tolérance, un nombre limité de nœuds accessibles pour la mesure et la nature non linéaire des équations de test. Pour ces raisons, dans de nombreux cas, les tests analogiques reposent sur une approche de boîte noire où les spécifications des circuits sont vérifiées sans prêter attention à la structure. En conséquence, le diagnostic des défauts des circuits analogiques présente un intérêt considérable, qui a donné lieu à de nombreuses publications au cours des dernières années, par exemple [12]-[16], [18]-[21], [23].

Bien qu'il existe de nombreuses méthodes proposées pour diagnostiquer les circuits électroniques analogiques, les plus populaires sont les techniques du dictionnaire de défauts. Mais au cours de ces dernières décennies, l'automatisation du diagnostic des défauts à l'aide des techniques de l'intelligence artificielle (IA) est devenue un outil de recherche important pour la résolution de nombreux problèmes dans ce domaine [25].

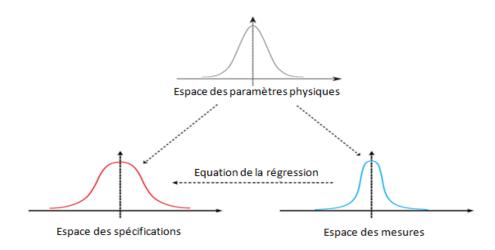

Dans notre projet, le travail porte sur l'application de la logique floue pour le diagnostic des fautes dans les circuits analogiques en prenant les dictionnaires de fautes

comme point de départ et en analysant la réponse du circuit sous test (CUT) dans le domaine du courant continu DC. Nous utiliserons une méthode de classification avec un système d'inférence floue (FIS). Le choix des paramètres du FIS (variables d'entrée et de sortie, types et paramètres des fonctions d'appartenances associées aux différents variables d'entrée et de sortie du système, la génération des règles d'inférence floue, ....) ont une importance majeure sur les performances du système d'inférence floue utilisé comme outil de diagnostic de fautes des circuits analogiques.

La thèse est structurée en 5 chapitres avec une introduction, une conclusion et des perspectives.

Dans le premier chapitre, les concepts de base du test des circuits et systèmes intégrés sont rappelés. Nous présentons le test dans le cycle de vie des circuits intégrés ainsi que les défauts rencontrés dans ces circuits. Nous décrivons également dans ce chapitre le classement de test et les différents types de test, fonctionnel, structurel et alternatif. On finira, par introduire le coût de test d'un circuit.

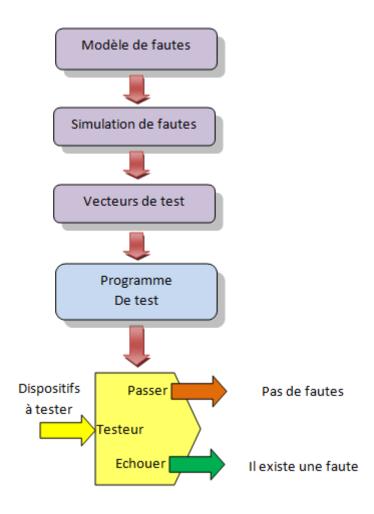

Le concept du Diagnostic de fautes des circuits analogiques est abordé dans le deuxième chapitre, en présentant dans une première partie, les différentes techniques de modélisation et de simulation de fautes, ainsi que les techniques de la génération de vecteurs de test. Dans une deuxième partie, nous traitons en détails les différentes techniques employées pour le diagnostic de fautes des circuits analogiques et plus particulièrement la simulation avant test (SBT) et la simulation après test (SAT).

Dans le troisième chapitre, nous rappelons en premier lieu les principes de base de la logique floue précédés d'un bref historique. Puis nous étalons une présentation des différentes étapes de la conception d'un système d'inférence floue à savoir la fuzzification, les règles floues et la défuzzification.

Quant au quatrième chapitre, la pièce maitresse est donnée à la mise au point de la stratégie de test en mode DC pour la détection de fautes catastrophiques des circuits analogiques. La simulation de fautes par le moyen de PSPICE y a fait partie et a permis l'établissement du dictionnaire de fautes en mode DC pour des signaux de tensions.

L'amélioration de la détection s'est rendue possible par l'usage du mode DC mais basé sur le courant d'alimentation comme paramètre de test.

Nous terminons le document avec un cinquième chapitre dédié aux résultats obtenus lors de l'application de la méthode proposée sur deux exemples d'application. Un système basé sur la logique floue est utilisé à cette fin et une comparaison entre les résultats obtenus dans ce chapitre et ceux du chapitre 4 est présentée.

En fin de cette thèse une conclusion parachèvera le travail entrepris tout en précisant les points positifs qui en découlent suivis des conseils et recommandations qu'il faut prendre en considération dans des futurs travaux de recherche. Cette partie concluante est suivie de quelques perspectives présentées à la fin de ce travail.

# Chapitre 1

## CONCEPTS DE BASE DU TEST DES CIRCUITS ET SYSTEMES INTEGRES

| Chapítre |  |

|----------|--|

# CONCEPTS DE BASE DU TEST DES CIRCUITS ET SYSTEMES INTEGRES

#### 1.1. Introduction

L'évolution de la technologie des circuits intégrés et la miniaturisation des transistors ont permis de réaliser des systèmes de plus en plus complexes sur une seule puce [1]. La croissance constante de l'industrie mondiale des semi-conducteurs au cours des dernières décennies a été stimulée par la demande d'amélioration des performances et des fonctionnalités à moindre coût. Cette croissance a été principalement facilitée par l'évolution continue de la technologie de fabrication des semi-conducteurs [2]. Selon la fameuse loi de Moore (figure 1.1), l'échelle d'intégration des circuits intégrés a doublé tous les 18 mois. Un exemple simple de cette tendance est le passage de l'intégration à petite échelle (SSI) (Small Scale Integration) à l'intégration à très grande échelle (VLSI) (Very Large Scale Integration). Dans les années 1980, le terme VLSI était utilisé pour les puces ayant plus de 100 000 transistors et a continué à être utilisé au fil du temps pour désigner les puces ayant des millions et maintenant des centaines de millions de transistors. En

1986, la première mémoire vive (RAM) de mégabit contenait plus d'un million de transistors. Les microprocesseurs produits en 1994 contenaient plus de 3 millions de transistors. Les composants VLSI avec plusieurs millions de transistors sont couramment utilisés dans les ordinateurs et les appareils électroniques d'aujourd'hui. C'est le résultat direct de la diminution constante des dimensions des transistors et des fils d'interconnexion, avec les technologies submicroniques actuelles basées sur des dimensions de quelques nanomètres seulement [3]. Il est primordial d'accompagner cette tendance à l'intégration et à la miniaturisation par une plus grande fiabilité et sûreté de fonctionnement.

La réduction de la taille des composants augmente la probabilité qu'un défaut de fabrication dans le CI entraînera une puce défectueuse. Un très petit défaut peut facilement entraîner un transistor ou un fil d'interconnexion défectueux lorsque la taille de l'élément est inférieure à 100 nm. De plus, il suffit qu'un seul transistor ou un fil défectueux pour que l'ensemble de la puce ne fonctionne pas correctement. Par conséquent, des tests sont nécessaires pour garantir des produits exempts de défauts. Il est également nécessaire de tester les composants à différentes étapes du processus de fabrication [4]. Par exemple, pour produire un système électronique, nous devons produire des circuits intégrés, utiliser ces circuits intégrés pour assembler des cartes de circuits imprimés (PCB) printed circuit boards, puis utiliser les PCB pour assembler le système.

Le test des circuits intégrés (ICs) est devenu une tâche essentielle dans l'industrie des semiconducteurs. Le développement d'approches et d'outils pour la génération et l'application des stimuli de test (ou de vecteurs de test) pour détecter le dysfonctionnement des dispositifs (ou des circuits), et localiser les fautes ou les erreurs de conception, nécessite un grand effort dans la recherche en raison de l'évolution rapide des technologies des semi-conducteurs. [5], Les sections suivantes décrivent brièvement les enjeux du test des circuits intégrés.

Figure 1.1. Représentation de la loi de Moore avec l'exemple des µP d'Intel.

#### 1.2. Notions de base du test

Le processus de conception des systèmes électroniques dépend des efforts de nombreux ingénieurs et techniciens. Une conception devient un dispositif physique après l'exécution des processus de fabrication qui tient compte de plusieurs tâches et matériaux afin de devenir le produit final. En général, dans un lot de fabrication, une conception unique est répétée plusieurs fois au cours du processus de fabrication, ce qui permet de réduire les coûts [6]. Pendant l'étape de fabrication dans les salles blanches, des défauts peuvent se produire (par exemple un court-circuit entre deux lignes métalliques parallèles ou entre les deux bornes d'un composant, un circuit-ouvert qui coupe la ligne métallique reliant deux composants etc.). Ces types de défauts rendent le circuit défectueux [7]. Le test des circuits électroniques peut intervenir à différents stades de la vie d'un circuit, de la conception jusqu'à l'utilisation dans l'application finale en passant par les différentes phases de production [9], afin de s'assurer que les circuits mis sur le marché donneront satisfaction au client en termes de fonctionnalité et de fiabilité [7].

Un comportement inexact du circuit, c'est-à-dire non conforme au comportement attendu, est défini par l'ensemble des termes suivants : défauts, erreurs et fautes [10]. Un lecteur peut trouver que ces termes sont parfois utilisés de manière confuse dans la littérature sur les tests. Une large étude et analyse de ces concepts a été faite dans [11]. Dans ce manuscrit, nous les utiliserons selon les définitions suivantes.

#### 1.2.1. Défauts

Selon [6] [10] [12], Le défaut (aussi appelé défaillance) dans les systèmes électroniques est défini comme suit :

« La différence involontaire entre l'implantation réelle et la conception physique prévue du système»

Un défaut peut être une impureté sur la structure de silicium reliant un fil à une source de tension, ou à la terre ainsi que d'autres fils résultant d'un comportement erroné permanent. Habituellement, dans les circuits VLSI, ils ne peuvent pas être mappés à un seul défaut, car ils peuvent produire des comportements différents. Par exemple, une particule métallique microscopique mal placée reliant une sortie à une source de tension produit un blocage à 1, alors que si elle est connectée à la terre, la sortie produit un blocage à 0. Bien qu'il s'agisse du même défaut, un fragment de métal égaré, il produit des situations différentes résultant de comportements défectueux différents. Pour cette raison, les défauts ne peuvent pas être directement transformés en défauts spécifiques.

Une autre situation qui peut se produire, des défauts peuvent être induits par une autre source provenant de l'environnement comme : les particules de rayonnement, les champs magnétiques, les températures élevées ou basses, et le stress physique. Dans ce cas, le défaut est transitoire et ne modifie que momentanément la structure physique (ou son fonctionnement), juste assez pour produire ou non un défaut transitoire [6].

Les défauts les plus courants sont :

- **1.** Défauts du procédé de fabrication: fenêtres de contact manquantes, transistors parasites, rupture d'oxyde, etc.

- 2. Défauts du matériau : défauts de volume (fissures, imperfections cristallines), impuretés du matériau, etc.

- 3. Défauts du vieillissement : rupture diélectrique, électromigration, etc.

- 4. Défauts du boîtier après encapsulation: dégradation du contact, étanchéité du boîtier, etc.

- **5.** Défauts induits par l'environnement: particules de rayonnement, humidité, vibrations, etc.

#### **1.2.2. Fautes**

La représentation du défaut à un degré d'abstraction supérieur, est appelée faute, La différence entre un défaut et un faute est assez subtile. Ce sont les imperfections du matériel et de la fonction, respectivement [11].

Une faute liée par exemple à un défaut de fabrication ou au vieillissement du circuit est dite *permanente*.

Certaines fautes peuvent aussi être *transitoires*, par exemple une faute induite par l'impact d'une particule dans un circuit combinatoire, qui entraîne un pic de courant et la modification du niveau logique d'un signal ; au bout d'un certain temps, l'effet dû au passage de la particule va s'annuler et la faute disparaît. Certains types de fautes peuvent aussi être *intermittents* et n'apparaître que sous certaines conditions [12].

#### **1.2.3. Erreurs**

Un signal de sortie erroné produit par un système défectueux s'appelle une erreur. Une erreur est un "effet" dont la cause est un "défaut" [11].

Une **défaillance** survient ensuite si cette erreur se propage à l'extérieur du circuit et induit un dysfonctionnement, c'est-à-dire un écart inacceptable par l'utilisateur entre la fonction spécifiée et celle actuellement délivrée par le circuit. La figure 1.2 présente les différents niveaux d'abstraction du défaut [12] [13].

Figure 1.2. Différents niveaux d'abstraction du défaut

#### 1.3. Le test dans le cycle de vie des circuits intégrés

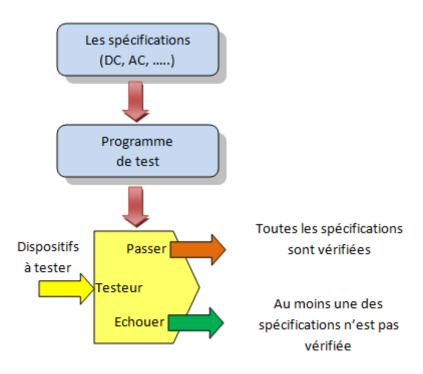

Le test consiste généralement à appliquer un ensemble de stimuli de test aux entrées du circuit sous test (CUT) tout en analysant les réponses de sortie, comme illustré à la Figure 1.3.

Les circuits qui produisent les réponses de sortie correctes pour tous les stimuli d'entrée réussissent le test et sont considérés comme exempts de défauts. Les circuits qui ne produisent pas une réponse correcte à n'importe quel moment de la séquence de test sont supposés défectueux [14].

Figure 1.3. Approche de base du test

Les tests sont effectués à diverses étapes qui constituent le cycle de vie du circuit, on distingue ainsi deux étapes principales pendant La fabrication d'un circuit intégré, une étape de conception du circuit et une étape de fabrication (voir figure 1.4). Dans chacune des étapes, un test doit être effectué. Dans la première étape, le test à effectuer est appelé test de validation ou test de caractérisation. Dans la deuxième étape, le test à effectuer est un test de production. Dans la présente section, nous examinons ces divers types de tests, en commençant par le test de caractérisation. [1] [5] [15] [16]

#### 1.3.1. Le test de caractérisation.

Le test de caractérisation est réalisé sur les premiers prototypes du circuit fabriqués à l'issue de la phase de conception [16], Il s'agit d'un test fonctionnel devant vérifier si les performances du circuit correspondent à celles prévues (du cahier de charges) [18]. Il est appelé aussi test de vérification. Cette forme de vérification est effectuée lors d'une nouvelle conception de circuit avant d'être transformé en produit fini, il s'agit de s'assurer de son bon état et que ce produit répond parfaitement à toutes les spécifications possibles [19].

Figure 1.4. Cycle de conception et de fabrication des circuits intégrés et la place du test dans ce cycle [1] [5] [18]

#### 1.3.2. Le test de production.

Le test de production des CIs a pour but de vérifier que les processus de fabrication et d'assemblage se sont déroulés correctement, et garantir ainsi le fonctionnement attendu des circuits finis [20]. Le test de production se doit de détecter les défauts de fabrication des circuits et ainsi de différencier les bons circuits des mauvais [16].

Le test de production se déroule de la façon suivante : à l'aide d'équipements dédiés au test, un ensemble de stimuli est appliqué en entrée du circuit et les réponses obtenues en sortie sont collectées. Si les réponses sont égales à celles attendues, le circuit est déclaré sain et peut être délivré au client. Par contre, si le circuit présente des erreurs, il est marqué comme défectueux et sera donc rejeté [15], il n'est plus possible de réparer les circuits défectueux, on n'a pas besoin de faire un diagnostic de tous les circuits rejetés [1].

#### 1.4. Les défauts dans les circuits intégrés

Un ensemble électronique est constitué d'un assemblage de composants de différentes natures, associés pour remplir une certaine fonction définie dans un cahier de charge. Il s'agit en général d'un ensemble de cartes imprimées équipées de composants passifs où actifs de différentes types comme résistances, capacités, amplificateurs, transistor, diodes ... etc.

Il ne sert à rien de construire des ensembles électroniques complexes utilisant les technologies les plus avancées à base des circuits analogiques où numérique, si l'on ne dispose pas de moyens de contrôle de leur bon fonctionnement. Un de ces moyens s'effectue au niveau processus de fabrication afin de confirmer la qualité de ces circuits ou dans le cas défavorable permettre de détecter les défauts avant que le produit ne soit lancé au marché [19].

La grande complexité de la nouvelle génération de circuits et de systèmes intégrés, combinée avec le développement des technologies, la haute vitesse de fonctionnement, la consommation basse d'énergie, la haute densité de mise en boite et de réduction du temps du cycle de conception, a rendu extrêmement difficile et cher le test de systèmes électroniques et le diagnostique des parties défectueuses en utilisant les méthodes de test traditionnelles. Cette situation s'empirera dans un avenir proche, lorsqu'un grand nombre de puces seront conçues avec des blocs analogiques et digitaux complexes et hétérogènes.

Le plus souvent, les défauts rencontrés dans les circuits intégrés proviennent de deux sources différentes à savoir les défauts provenant des erreurs de conception et les défauts de fabrication. Tous les deux peuvent entraîner un dysfonctionnement total du circuit ou à des degrés moindres.

Les défauts de fabrication d'un circuit intégré sont généralement de deux types : les défauts dont l'origine provient de l'environnement de fabrication et les défauts causés par une variation du processus de fabrication.une particule de poussière qui se dépose sur la tranche de silicium du circuit en cours de sa fabrication constitue un exemple de défaut dû à l'environnement. Un exemple de défaut causé par une variation de processus de fabrication est un mauvais alignement des masques.

Pour bien comprendre Les défauts dans les circuits intégrés, il est nécessaire de connaître les sources provoquant les fautes (section 1.4.1). Les classes des fautes sont décrites en (section 1.4.2).

#### 1.4.1. Sources des fautes

On rencontre le plus souvent des circuits électroniques tels que les diodes, les transistors, les circuits qui tombent en panne même si apparemment ces composants n'ont subit aucune usure. Cela est du à plusieurs mécanismes qui se manifestent au niveau de leur structure interne. Le procédé de fabrication est généralement la cause principale de la présence des fautes, que ce soit après fabrication ou bien après une durée de vie du circuit. Les fautes peuvent être aussi provoquées par le design et sont sensées être corrigées après la vérification des prototypes [7] [19].

Le Tableau 1.1 résume les mécanismes de défaillances observés sur les dispositifs fabriqués, ainsi que les défauts qu'ils sont susceptibles d'engendrer. Ils ont étés classés suivant qu'ils proviennent de la fabrication ou qu'ils se produisent lors de l'utilisation [21].

#### 1.4.2. Classification des fautes

L'étape de conception de circuits peut être entachée d'erreurs qui devraient être détectées dans l'étape de vérification [22]. Des erreurs peuvent aussi être introduites dans l'étape de production. Le but ultime du test est de détecter les circuits défectueux compte tenu de ces erreurs.

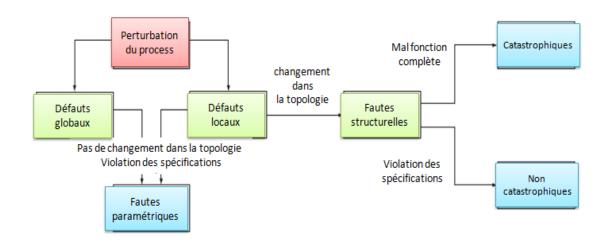

Les variations du processus de fabrication engendrent deux types de défauts : les défauts globaux et les défauts locaux (Figure 1.5). Un défaut global correspond à une variation systématique d'un même paramètre. Par exemple, une variation hors tolérance de la tension de seuil de tous les transistors du circuit est représentative d'un défaut global.

| Mécanismes de défaillances |                                     | Défauts                                                                                            |

|----------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------|

| Fabrication                | Lithographie                        | Défauts topologiques, courts circuits , circuits ouverts, variations paramétriques des topologies. |

|                            | Dépôts                              | Variation paramétriques : topologiques, mécaniques, thermiques.                                    |

|                            | Gravures des couches sacrificielles | Collage, sur-gravures, rugosité.                                                                   |

|                            | Séchage                             | Collage, non alignement, fracture.                                                                 |