#### الجمهورية الجزائرية الديمقراطية الشعبية

République Algérienne Démocratique et Populaire Ministère de L'Enseignement Supérieur et de la Recherche Scientifique

# UNIVERSITÉ FERHAT ABBAS - SETIF 1 FACULTÉ DE TECHNOLOGIE

### **THESE**

Présentée au département d'électronique

Pour l'obtention du diplôme de

#### **DOCTORAT EN SCIENCES**

Option: électronique

Par

ARABI Abderrazak

## **THÈME**

# Méthodes de diagnostic et de maximalisation de la couverture des fautes singulières fréquentes dans les circuits analogiques

#### Soutenue le 25/04/2019 devant le Jury:

| <b>BOUZIT Nacerdine</b>   | Professeur | Univ. Ferhat Abbas Sétif 1   | Président          |

|---------------------------|------------|------------------------------|--------------------|

| <b>BOUROUBA Nacerdine</b> | Professeur | Univ. Ferhat Abbas Sétif 1   | Directeur de thèse |

| AMARDJIA Noureddine       | Professeur | Univ. Ferhat Abbas Sétif 1   | Examinateur        |

| AIDEL Salih               | Professeur | Univ. B.I. Bordj bouarréridj | Examinateur        |

| KHEDROUCHE Djamel         | Professeur | Univ. M.B. M'sila            | Examinateur        |

| AIT KAKI Abdelaziz        | M.C.A      | Univ. L.B.M. Oum El-bouaghi  | Examinateur        |

#### Remerciements

Tout particulièrement louange et grand merci à Dieu le Tout –puissant qui par bonté et sa générosité inégalable, m'a procuré savoir et volonté tant rechercher pour parachever mon travail et ma thèse de doctorat en sciences.

Je remercie ensuite mon encadreur Monsieur **Nacerdine BOUROUBA**, Professeur à l'université Ferhat Abbas Sétif 1, qui n'a ménagé aucun effort pour que ma thèse voit le jour et dont les conseils et encouragements m'ont été très utiles dans la préparation de ce travail.

J'adresse également mes remerciements les plus vifs aux membres du jury, dont j'ai beaucoup d'estime et considération, qui m'ont fait l'honneur d'accepter de juger ce travail. En l'occurrence je cite Monsieur **BOUZIT Nacerdine**, Professeur à l'Université Ferhat Abbas Sétif 1, en tant que Président de Jury. Je tiens également à exprimer ma gratitude aux examinateurs:

- ❖ Monsieur **AIDEL Salih**, Professeur à l'Université de Mohamed Elbachir El-ibrahimi Bordj Bou Arreridj.

- Monsieur KHEDROUCHE Djamel, Professeur à l'Université Mohamed Boudiaf Msila.

- Monsieur AIT KAKI Abdelaziz, Maitre de conférences classe A à l'Université Larbi ben M'hidi Oum El-bouaghi.

- ❖ Monsieur **AMARDJIA Noureddine**, Professeur à l'Université Ferhat Abbas Sétif 1.

Mes remerciements vont bien sur à tous mes collègues qu'ils soient doctorants ou enseignants pour les marques de sympathie qu'ils n'ont cessé de me témoigner, sans oublier le soutien moral que j'ai de la part des Monsieurs : Dr. BELAOUT Abdesslam, SAHLI Abdesslam, Dr.TALBI Billel, LAIB Abdelbaset, BOUYAHIA Semcheddine, SBAIHI Messaoud et Dr.FERROURA Hamza .

# **Dédicaces**

A ma chère mère

A mon cher père

A ma femme, à mes enfants Zakaria et Serine

A mes frères Farid, Ilyes et Sami

A toutes mes sœurs

#### Résumé

Cette thèse porte sur l'application de nouvelles techniques au diagnostic, la détection et la classification des défauts dans les circuits intégrés analogiques, qui peuvent tomber en panne et se dégradent pendant la durée de fonctionnement. Ces derniers sont devenus de plus en plus nécessaires dans le monde de l'électronique. Cette nécessité est due à leurs importance dans les domaines de télécommunication, de l'avionique, du biomédical... Ce qui nécessite un diagnostic dont l'objectif principal est de fournir un outil automatique qui permet la détection précoce des défauts pour protéger les circuits, et de classifier le défaut en plus. Des techniques de test ont été appliquées à ces circuits analogiques à savoir le test fonctionnel, l'amélioration de la détection, la simulation des fautes. Pour le développement des algorithmes de classification de défauts dans les circuits analogiques, au début, une base de données est collectée en utilisant une simulation Monté Carlo en régime fréquentielle et transitoire, pour le circuit sain et fautif. Des classificateurs à base d'intelligence artificielle ont été construits, tels que les classificateurs neuronal et neuro-flou. Finalement, le diagnostic a été amélioré par l'introduction d'un nouveau classificateur (classificateur neuro-flou multi-classes). Ce dernier a été comparé à d'autres types de classificateurs, et s'est remarqué d'eux par son efficacité et sa précision.

*Mots clés*: detection des fautes ; classification des fautes ; classificateur neuro-floue; test des circuits analogiques.

#### **Abstract**

This thesis focuses on the application of new techniques to diagnosis, detection and classification of faults in analog integrated circuits, which can break down and degrade during the operating period. These circuits have become more necessary in the world of electronics. This need is due to its importance in the areas of telecommunication, avionics, biomedical... This requires a diagnosis that's the main purpose is to provide an automatic tool that allows early detection of faults to protect the circuits, and to classify this faults two. Test techniques have been applied to these analogue circuits, namely the functional test, the improvement of the detection, the simulation of faults. For the development of the algorithms of classification of faults in the analog circuits, at the beginning, a database is collected using a simulation mounted Carlo in frequency and transient domain, for the fault free and faulty circuit. Artificial intelligence-based classifiers have been constructed, such as neural and neuro-blur classifiers. Finally, the diagnosis was improved by the introduction of a new classifier (Multi-class neuro-blur classifier). This classifier was compared to other types of classifiers, and over classed to them by its efficiency and accuracy.

*Keywords:* fault detection; fault classification; neuro-fuzzy classifier; diagnostic; analog circuits test.

# **Sommaire**

Résumé

Liste des Figures

Liste des Tableaux

Liste des acronymes

| Chapitre1: Introduction                                      |    |

|--------------------------------------------------------------|----|

| 1.1 Contexte et motivation.                                  | 1  |

| 1.2 Classification des défauts.                              | 2  |

| 1.3 Classification des techniques de localisation des pannes | 3  |

| 1.3.1 Simulation avant test (SBT)                            | 3  |

| 1.3.1.1 Technique de dictionnaire de fautes                  | 4  |

| 1.3.1.2 L'approche statistique.                              | 4  |

| 1.3.2 Simulation après test(SAT)                             | 4  |

| 1.3.2.1 Technique d'identification des paramètres            | 5  |

| 1.3.2.2 Techniques de vérification des fautes.               | 5  |

| 1.3.2.3 Méthode d'optimisation.                              | 6  |

| 1.4 Diagnostic de défauts en analogique et en numérique      | 6  |

| 1.5 Problématique.                                           | 7  |

| 1.6 Organisation de la thèse.                                | 7  |

| 1.7 Contributions.                                           | 8  |

|                                                              |    |

| Chapitre 2: Etat de l'art test des circuits intégrés         |    |

| 2.1 Introduction.                                            | 9  |

| 2.2 Généralités                                              | 12 |

| 2.2.1 Définitions de la faute                                | 12 |

| 2.2.2 Types de fautes                                        | 13 |

| 2.2.3 Sources de fautes.                                     | 14 |

| 2.2.4 Simulation de fautes                                   | 15 |

| 2.3 Tâches des systèmes de diagnostic des fautes             | 15 |

| 2.4 Les différents types de test.                            | 16 |

| 2.4.1 Difficultés de test des circuits analogiques           | 17 |

| 2.4.2 Génération de test                                                  | 19 |

|---------------------------------------------------------------------------|----|

| 2.4.3 Classification des tests.                                           | 20 |

| 2.4.4 Couverture d'un test.                                               | 21 |

| 2.4.5 Qualité des tests.                                                  | 21 |

| 2.4.6 testabilité.                                                        | 21 |

| 2.5 Modélisation des fautes analogiques.                                  | 22 |

| 2.6 La simulation des fautes analogiques                                  | 23 |

| 2.7 Conclusion.                                                           | 26 |

|                                                                           |    |

| Chapitre 3: Modélisation des défauts dans les circuits intégrés           |    |

| 3.1 Introduction                                                          | 27 |

| 3.2 Sources de défauts dans les circuits intégrés                         | 29 |

| 3.2.1 Les erreurs de conception                                           | 29 |

| 3.2.2 Les défauts de fabrication.                                         | 29 |

| 3.3 Défaillances physiques et défauts de fabrication                      | 30 |

| 3.3.1 Mécanismes de défaillance                                           | 30 |

| 3.3.2 Classification de fautes                                            | 31 |

| 3.3.3 Défauts paramétriques et défauts fonctionnels                       | 34 |

| 3.4 Défauts des composants à semi-conducteurs                             | 34 |

| 3.4.1 Claquage de couches isolantes (Oxyde break down)                    | 35 |

| 3.4.2 Injection de porteurs chauds (Hot carrier injection)                | 35 |

| 3.4.3 Electromigration.                                                   | 35 |

| 3.4.4 Crevasse dans les couches de passivation ou les couches métallisées | 35 |

| 3.4.5 Coupure des fils de liaison                                         | 36 |

| 3.4.6 Corrosion par l'humidité.                                           | 37 |

| 3.4.7 Effet thyristor.                                                    | 37 |

| 3.5 Les fautes de type matériel/physique.                                 | 37 |

| 3.5.1 Faute permanente                                                    | 37 |

| 3.5.2 Faute transitoire (ou temporaire)                                   | 37 |

| 3.5.3 Faute intermittente                                                 | 38 |

| 3.6 Modélisation des fautes                                               | 38 |

| 3.7 Techniques de simulation des fautes                                   | 39 |

| 3.8 Modèles de fautes des circuits analogiques                     | 3         |

|--------------------------------------------------------------------|-----------|

| 3.8.1 Modélisation de fautes en analogique                         | 4         |

| 3.8.2 Génération de la liste de fautes                             | 4         |

| 3.8.3 La simulation de fautes.                                     | 4         |

| 3.9 Test de circuits analogiques et mixtes                         | 4         |

| 3.9.1 Le test fonctionnel de circuits analogiques.                 | 4         |

| 3.9.2 Les techniques de test structurel (test basé sur les fautes) | 4         |

| 3.10 Modèles de fautes des circuits numériques                     | 4         |

| 3.10.1 Simulation de fautes en numérique                           | 4         |

| 3.11 Simulation de fautes en numérique                             | 4         |

|                                                                    |           |

| Chapitre 4: Méthodes de detection et couverture des faute          | <u>es</u> |

| 4.1 Introduction                                                   | 4         |

| 4.2 Detection des fautes catastrophiques au niveau des transistors | 4         |

| 4.2.1 Exemple de circuit sous test                                 |           |

| 4.2.2 Structure des transistors utilisés                           | 5         |

| 4.2.3 Modèle de fautes à détecter                                  | 4         |

| 4.2.4 Principe de la méthode                                       | 5         |

| 4.2.5 Simulation du circuit sous test sous la faute F2             | 4         |

| 4.2.6. Simulation du circuit sous test sous la faute F5            | 4         |

| 4.2.7 Interprétation des résultats.                                | 4         |

| 4.3. Detection des fautes par l'analyse Monte-Carlo                | 4         |

| 4.3.1 Le circuit sous test.                                        | 4         |

| 4.3.2 L'analyse Monte-Carlo.                                       | 6         |

| 4.3.3 Contrôle de la sortie.                                       | 6         |

| 4.5.5 Controle de la sortie                                        | 6         |

| 4.3.4 Simulations et résultats                                     |           |

|                                                                    |           |

| 4.3.4 Simulations et résultats                                     | relle     |

| 5.1.1 Méthodes de détection et de classification existantes et leurs limitations | 71  |

|----------------------------------------------------------------------------------|-----|

| 5.1.2 Contributions.                                                             | 73  |

| 5.2 Les classifieurs basés sur l'intelligence artificielle                       | 73  |

| 5.2.1 Développement d'un classifieur neuro-flou multi-classes                    | 73  |

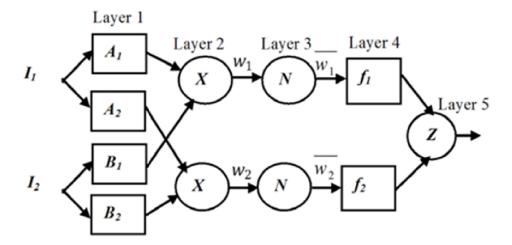

| 5.2.2 Principe du classifieur neuro-flou.                                        | 74  |

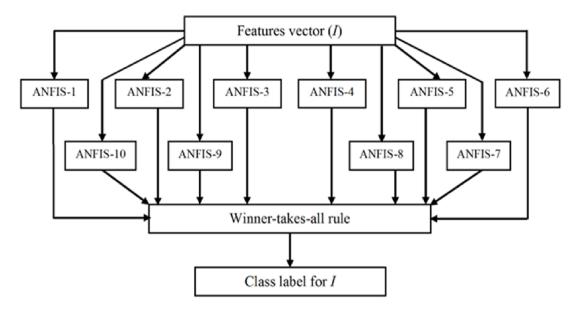

| 5.2.3 Approche de classification multi-classes                                   | 77  |

| 5.2.4 Critères d'évaluation de la performance des classifieurs                   | 78  |

| 5.3 circuits sous test et résultats de simulation                                | 79  |

| 5.3.1 Premier circuit sous test: le filtre passe-bande de Sallen – Key           | 79  |

| 5.3.1.1 Résultats de simulation                                                  | 80  |

| 5.3.1.2 Génération des entrées du classificateur                                 | 81  |

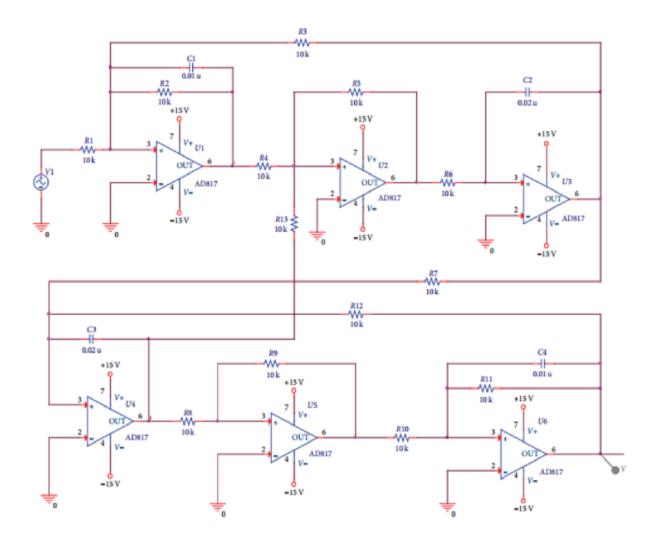

| 5.3.2 Deuxième circuit sous test: filtre passe-haut biquad à quatre opamp        | 83  |

| 5.3.3 Troisième circuit sous test: filtre leapfrog                               | 85  |

| 5.4 Résultats et discussions.                                                    | 87  |

| 5.4.1 Résultats pour le premier circuit sous test                                | 87  |

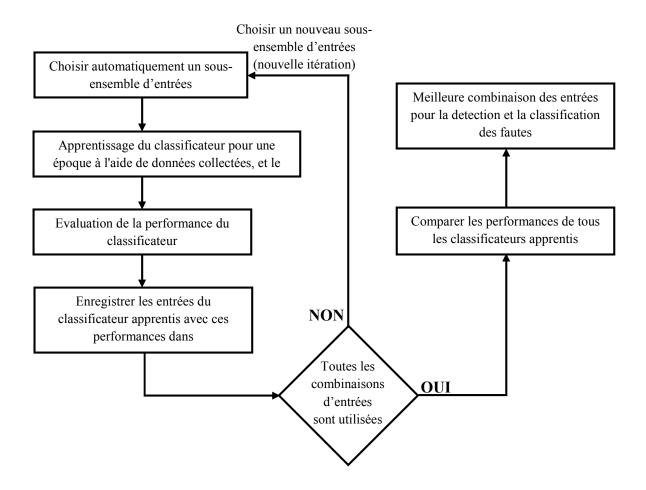

| 5.4.1.1 Reduction de nombre des entrées du classifieur                           | 87  |

| 5.4.1.2 Techniques de sélection des entrées.                                     | 88  |

| 5.4.1.3 Optimisation de type et du nombre des fonctions d'appartenance du        |     |

| classificateur ANFIS                                                             | 91  |

| 5.4.1.4 Classification des fautes par les réseaux de neurone artificiels         |     |

| (ANN)                                                                            | 94  |

| 5.4.2 Résultats pour le deuxième circuit sous test.                              | 95  |

| 5.4.3 Résultats pour le troisième circuit sous test.                             | 97  |

| 5.5 Conclusion                                                                   | 99  |

| Chapitre 6: Conclusion et travaux futurs                                         |     |

| 6.1 Conclusions                                                                  | 100 |

| 6.2 Travaux futurs                                                               | 102 |

| Bibliographie                                                                    |     |

| Liste des publications                                                           |     |

# **Liste des Figures**

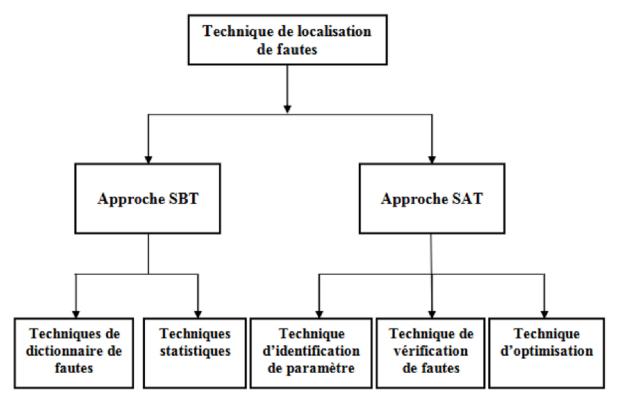

| Figure 1.1: Techniques de classification de fautes                                       | 3  |

|------------------------------------------------------------------------------------------|----|

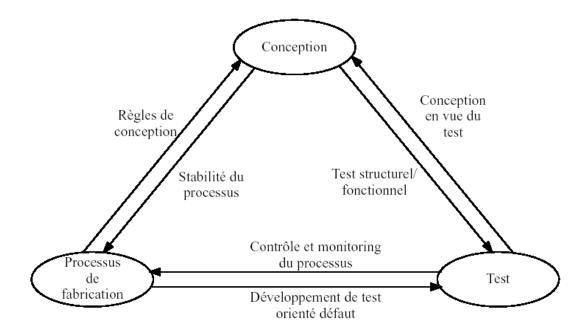

| Figure 3.1: Interaction entre conception, test et processus de fabrication en vue d'une  | •  |

| production de qualité                                                                    | 28 |

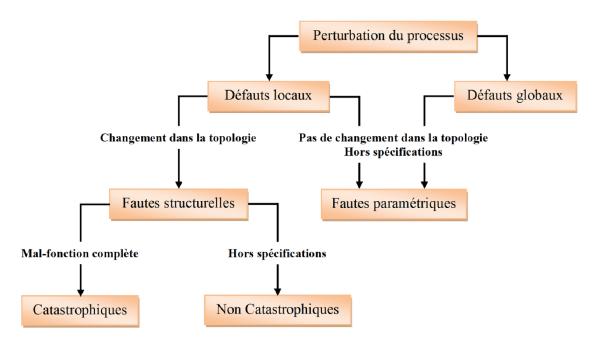

| Figure 3.2: Classification des fautes analogiques                                        | 33 |

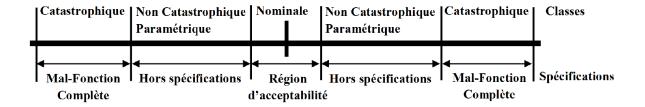

| Figure 3.3: Spécifications reliées aux classes de fautes                                 | 34 |

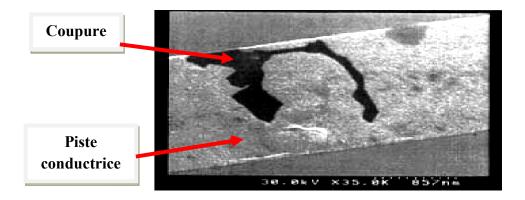

| Figure 3.4: Electromigration.                                                            | 35 |

| Figure 3.5: Fissure dans les couches de passivation                                      | 36 |

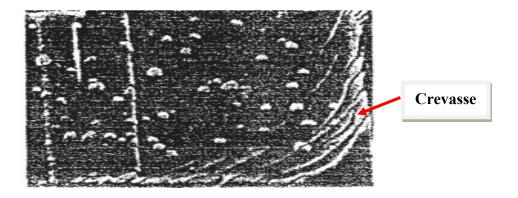

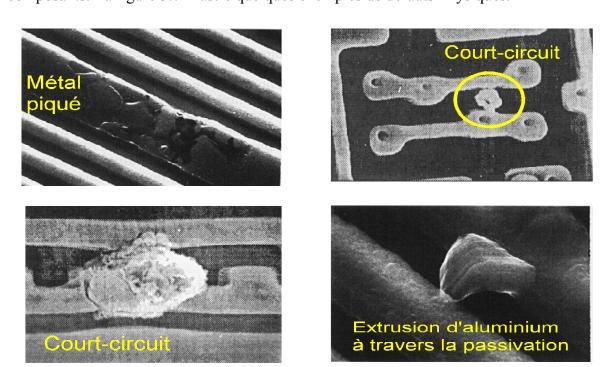

| Figure 3.6: Réalisation des liaisons : a) coupe des circuits encapsulés, b) détail de la |    |

| liaison par fil d'Or, c) aspect d'une liaison en fil d'Aluminium collé aux               |    |

| ultrasons                                                                                | 36 |

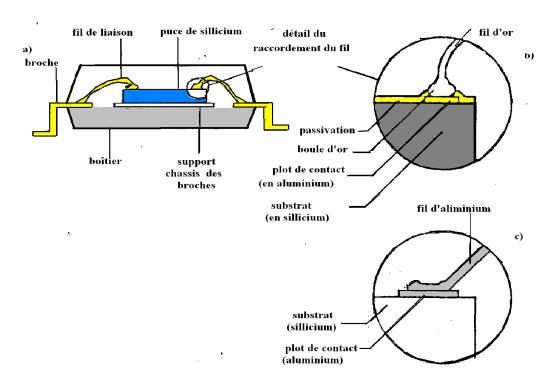

| Figure 3.7: Exemples de défauts physiques                                                | 40 |

| Figure 3.8: fautes affectant un circuit numérique.                                       | 45 |

| Figure 4.1: Filtre passe-bas de deuxième ordre                                           | 48 |

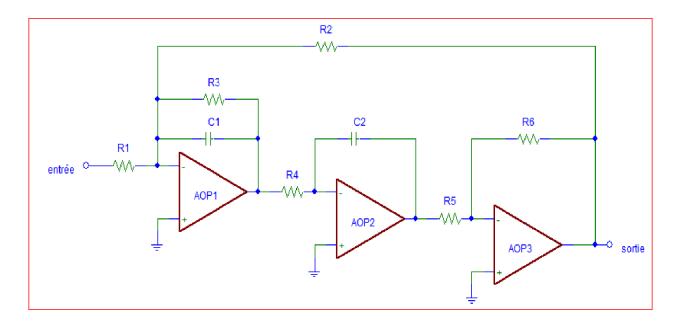

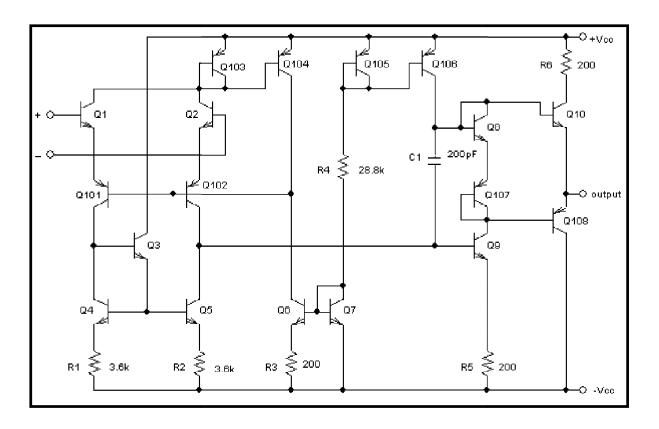

| <b>Figure 4.2:</b> Schéma interne de l'amplificateur opérationnel μA741                  | 49 |

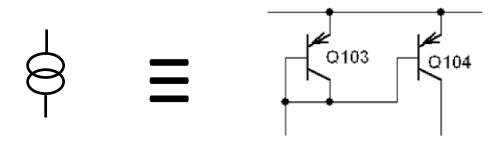

| <b>Figure 4.3:</b> Polarisation de l'étage d'entrée (Q103 monté en diode)                | 49 |

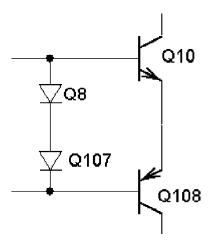

| Figure 4.4: Polarisation de push-pull                                                    | 50 |

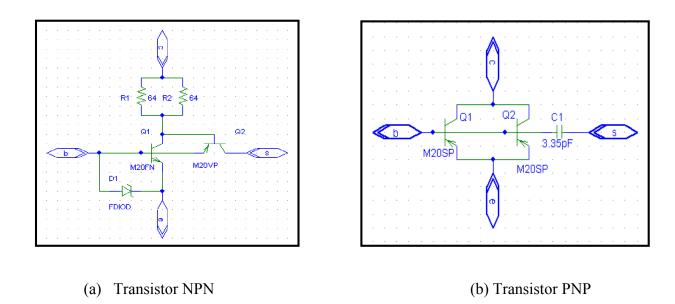

| Figure 4.5: Structure des transistors                                                    | 51 |

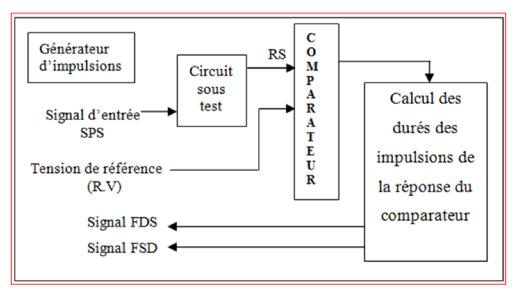

| Figure 4.6: Diagramme de la méthode de test proposée.                                    | 52 |

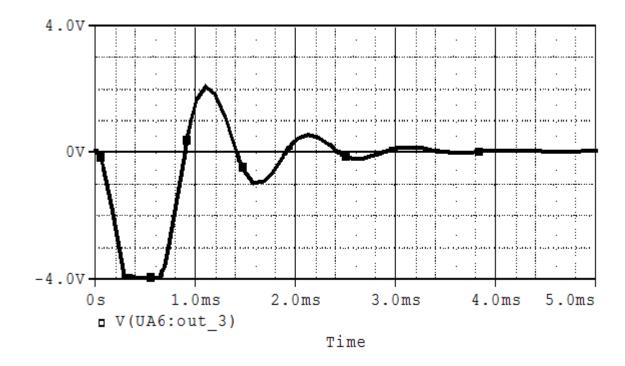

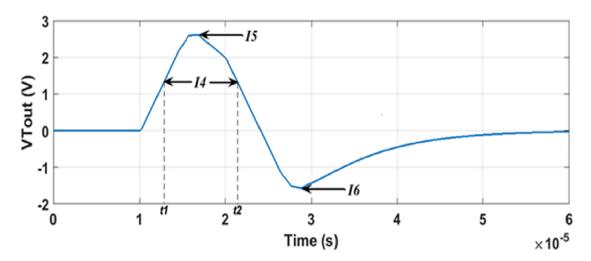

| Figure 4.7: Réponse temporelle du circuit sous test                                      | 54 |

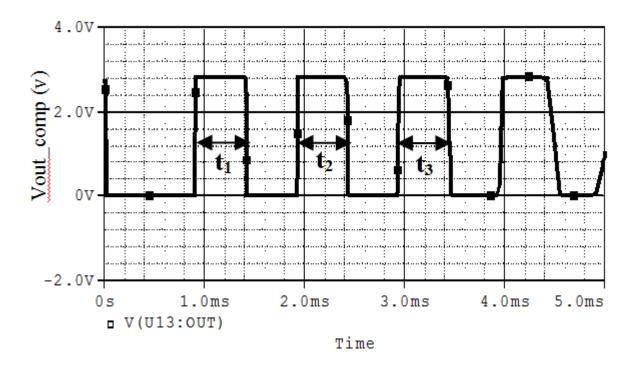

| Figure 4.8: Réponse du comparateur en absence des fautes.                                | 55 |

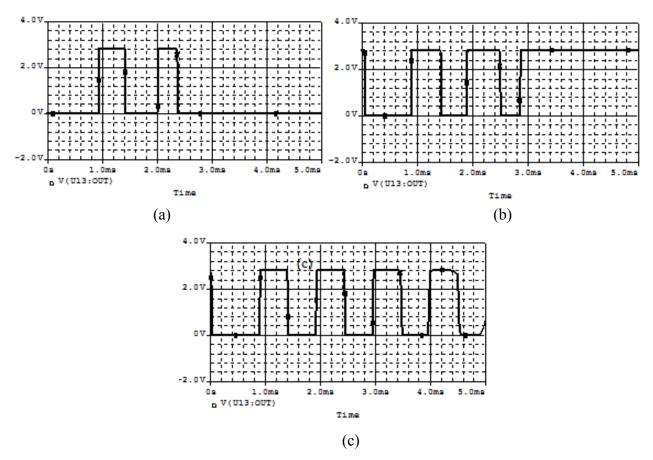

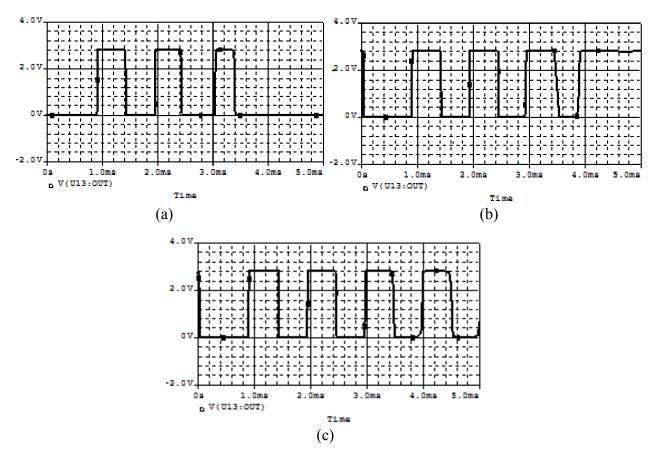

| Figure 4.9: Réponse du comparateur sous la faute F2.                                     | 56 |

| Figure 4.10: réponse du comparateur sous la faute F5.                                    | 57 |

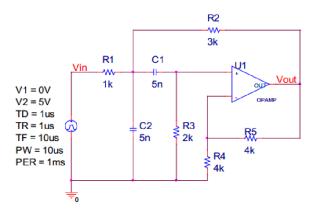

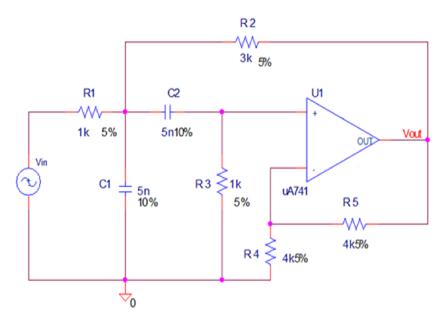

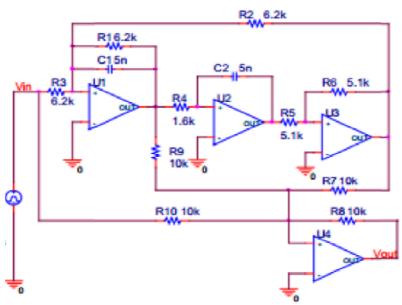

| Figure 4.11: schéma du filtre passe bande de Sallen-Key.                                 | 59 |

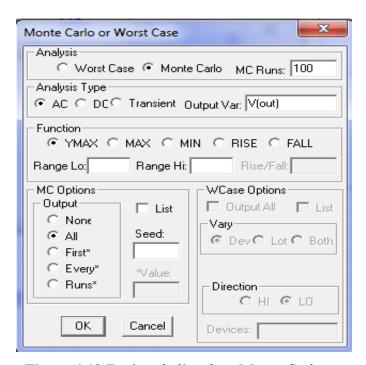

| Figure 4.12: Fenêtre de l'analyse Monte-Carlo                                            | 60 |

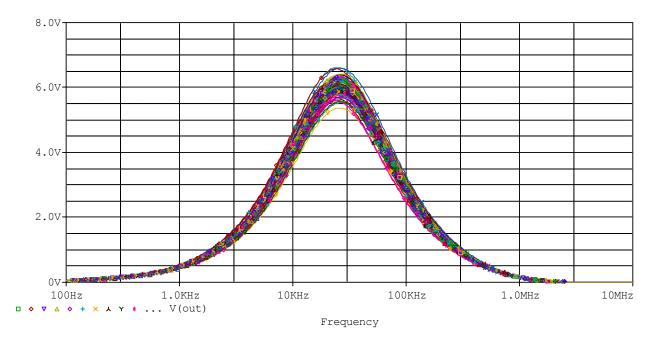

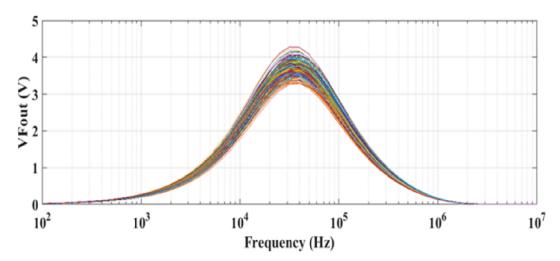

| Figure 4.13: réponses fréquentielles du filtre passe bande de Sallen-Key sans fautes                          |   |

|---------------------------------------------------------------------------------------------------------------|---|

| Pour 100 itérations                                                                                           | 6 |

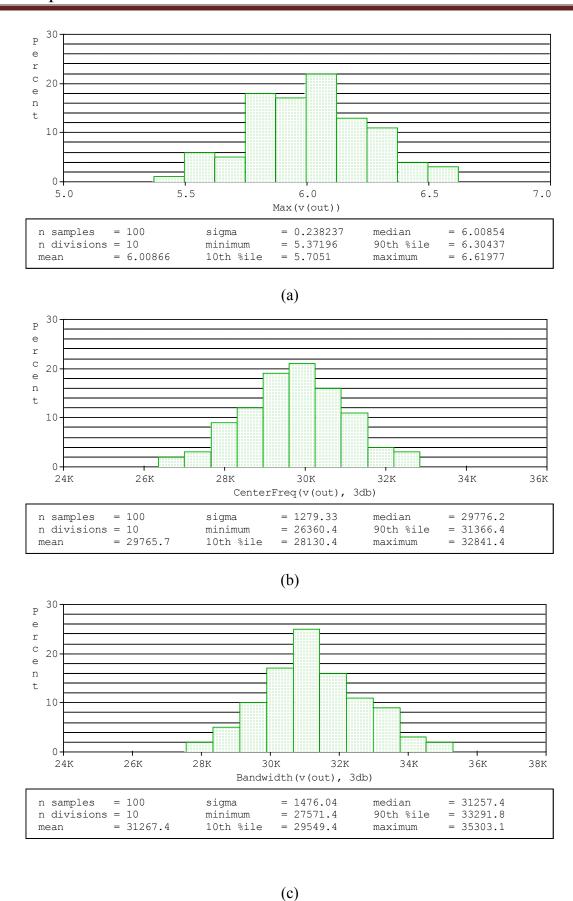

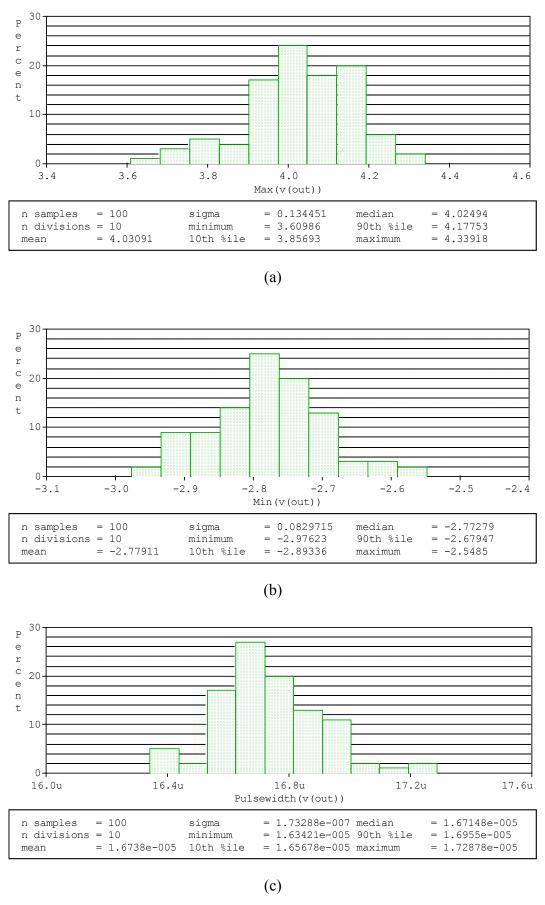

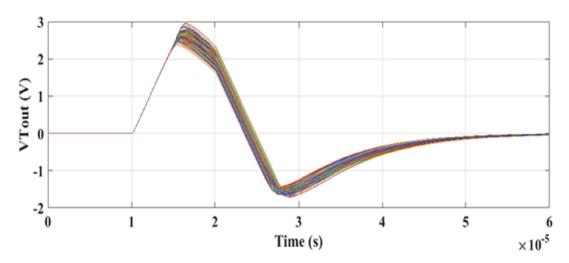

| Figure 4.14: Histogrammes correspondants aux paramètres de test du CUT sans fautes                            | 6 |

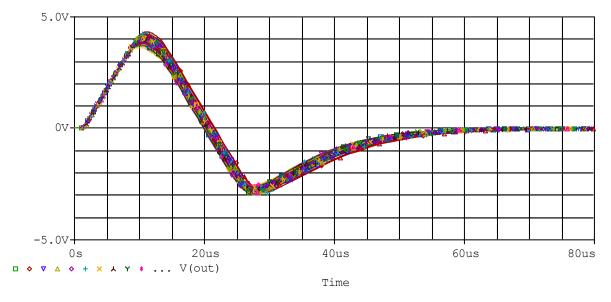

| <b>Figure 4.15:</b> réponses temporelles du filtre passe bande de Sallen-Key sans fautes Pour 100 itérations. | 6 |

| Figure 4.16: Histogrammes correspondants aux paramètres de test du CUT sans fautes                            | 6 |

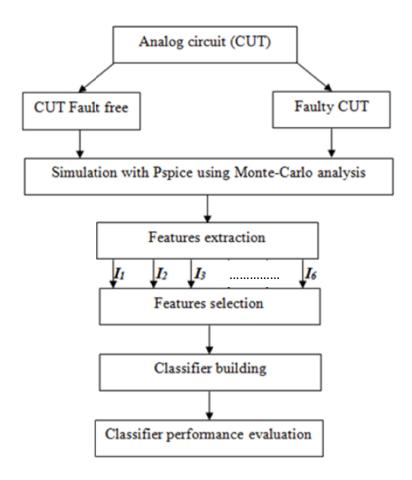

| Figure 5.1: Processus d'un classificateur des fautes du circuit sous test                                     | 7 |

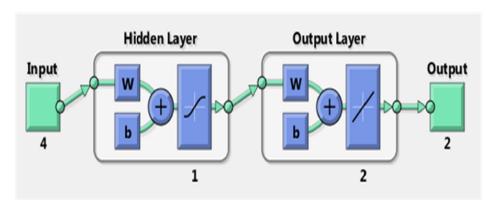

| Figure 5.2: Modèle de l'architecture ANFIS avec deux entrées, une sortie et deux règles.                      | 7 |

| Figure 5.3: Concept des classificatrices neuro-flou multi-classes                                             | 7 |

| Figure 5.4: Schéma du filtre passe-bande de Sallen-Key                                                        | 7 |

| Figure 5.5: Réponse fréquentielle du circuit sous test sans fautes                                            | 8 |

| Figure 5.6: Réponse temporelle du circuit sous test sans fautes                                               | 8 |

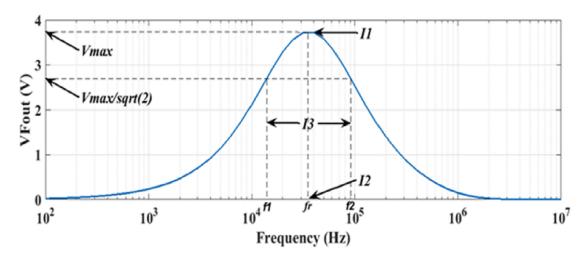

| Figure 5.7: Extraction des entrées à partir de la réponse fréquentielle du circuit sous test sans fautes      | 8 |

| <b>Figure 5.8:</b> Extraction des entrées à partir de la réponse temporelle du circuit sous test sans fautes  | 8 |

| <b>Figure 5.9:</b> Filtre biquad passe-haut à quatre amplificateurs opérationnels                             | 8 |

| Figure 5.10: Schéma du filtre leapfrog                                                                        | 8 |

| Figure 5-11: Vue de la méthode proposée pour la réduction des entrées du classificateur.                      | 8 |

| Figure 5 12: diagramme des réseaux de neurone artificiels (ANN)                                               | C |

## Liste des Tableaux

| Tableau 3.1: Différents types de fautes et composants affectés                        | 40  |

|---------------------------------------------------------------------------------------|-----|

| Tableau 4.1: fautes injectées dans le circuit sous test                               | 53  |

| Tableau 4.2: Durées des impulsions de la sortie du comparateur pour le circuit sous   |     |

| test sain                                                                             | 55  |

| Tableau 4.3: Variations des durées d'impulsions de la réponse du comparateur          | 58  |

| Tableau 4.4 : Détection des fautes paramétriques par les paramètres de la réponse     |     |

| fréquentielle du circuit sous test                                                    | 64  |

| Tableau 4.5: Détection des fautes catastrophiques par les paramètres de la réponse    |     |

| fréquentielle du circuit sous test                                                    | 65  |

| Tableau 4.6: Détection des fautes paramétriques par les paramètres de la réponse      |     |

| temporelle du circuit sous test                                                       | 68  |

| Tableau 4.7: Détection des fautes catastrophiques par les paramètres de la réponse    |     |

| temporelle du circuit sous test                                                       | 69  |

| Tableau 5.1: Valeurs nominales et altérées par fautes des composants du filtre passe- |     |

| bande de Sallen-Key                                                                   | 80  |

| Tableau 5.2: Valeurs nominales et fautives du Filtre biquad passe haut à quatre       |     |

| amplificateurs opérationnels                                                          | 84  |

| Tableau 5.3: Valeurs nominales et fautives pour le filtre leapfrog.                   | 86  |

| Tableau 5.4: Selection des entrées pour les classificateurs du filtre passe bande de  |     |

| Sallen_Key                                                                            | 91  |

| Tableau 5.5: Erreur RMS et type des fonctions d'appartenance durant le processus      |     |

| d'optimisation                                                                        | 92  |

| Tableau 5.6: Types et nombre de fonctions d'appartenance optimisées                   | 93  |

| Tableau 5.7: Comparaison entre le classificateur neuro flou multi-classes et celui de |     |

| réseaux de neurone artificiels pour le filtre passé bande de Sallen Key               | 0.4 |

| Tableau 5.8: Comparaison entre le classificateur neuro flou multi-classes et autres   | 94  |

|                                                                                       | 95  |

| Tableau | <b>5.9:</b> Comparaison entre le classificateur neuro-flou multi-classes et le |    |

|---------|--------------------------------------------------------------------------------|----|

|         | classificateur neuronal pour le filtre biquad passe-haut à quatre              |    |

|         | amplificateurs opérationnels                                                   | 96 |

| Tableau | 5.10: Comparaison sur la précision de classification entre la méthode          |    |

|         | proposée et les autres méthodes précitées pour le filtre passe-haut à          |    |

|         | quatre amplificateurs                                                          | 97 |

| Tableau | 5.11: Comparaison entre le classificateur neuro-flou multi -classes et le      |    |

|         | classificateur ANN pour le filtre leapfrog                                     | 98 |

# Liste des acronymes

AC Alternative Current

AI Artificial Intelligence

ANFIS Adaptive Neuro-Fuzzy Inference System

ANN Artificial Neural Network

AOP Amplificateur Opérationnel

ATPG Automatic Test Pattern Generation

BILBO Built in Logic Block Observer

BIST Built In Self Test

BP Back Propagation

BW Band Width

CFOA Current Feedback Operational Amplifiers

CI Circuits Intégrés

CUT Circuit Under Test

DC Direct Current

DFT Design For Testability

FC Fault Classification

FC Fuzzy Classifier

FD Fault Detection

FDC Fault Detection and Classification

FDM Fault Detection Method

FDS Fault Detection Signal

FF Fault Free

FIS Fuzzy Inference System

FRFT Fractional Fourier Transform

FSD Fault Signature Data

FWT Fractional Wavelet Transform

KPCA Kernel Principal Component Analysis

LM Levenberg-Marquardt

LSI Large Scale Integration

LSSD Level Sensitive Scan Design

MC-NFC Multiclass Neuro-Fuzzy Classifier

MF Membership Function

MLP Multilayer Perceptron

MSI Medium Scale Integration

NFC Neuro-Fuzzy classifier

PCM Process Control Monitoring

PTDM Pulses Time Durations Measurement

PW Pulse Width

$R^2$  Correlation coefficients

RMSE Root Mean Square Error

RMSE Root Mean Square Error

RS Response Signal

SAT Simulation After Test

SBT Simulation Before Test

SOS System On Chip

SPS Square Pulse Sequence

SSE Sum Square Error

SSE Sum squared error

SSI Small Scale Integration

SVDD Support Vector Data Description

SVM Super Vector Machine

T-S Takagi-Sugeno

VLSI Very Large Scale Integration

VVRKFA Vector-Valued Regularized Kernel Function Approximation

# Chapitre 1

Introduction

## **CHAPITRE 1**

# Introduction

#### 1.1. Contexte et Motivation

Le diagnostic des défauts des circuits intégrés analogiques a gagné une grande attention étendue dans le domaine des essais automatisés à l'aide des ordinateurs.

Les progrès de la technologie des systèmes sur puce (SOC) ont eu pour conséquence d'accroître l'importance des circuits analogiques, ce qui les a conduits à la technologie principale des circuits intégrés. La complexité accrue des circuits intégrés est due à l'amélioration réalisée dans la technologie Deep Sub micron et à la coexistence de circuits analogiques et numériques appelés conception de signaux mixtes. Cela a fait des tests une tâche très difficile qui doit être effectuée sur de très petites puces ayant des fonctionnalités complexes. Les méthodes de test et de diagnostic sont classées en:

- 1- Circuits numériques

- 2- Circuits analogiques

- 3- Circuits de signaux mixtes.

Dans les circuits numériques, de nombreuses méthodes de diagnostic ont été développées. Certaines de ces méthodes sont comme suit [1]:

- (a) D-algorithme

- (b) Conception d'un balayage sensible de niveau (Level Sensitive Scan Design LSSD)

- (c) norme IEEE 1149.1

- (d) implémentation dans un bloc observateur logique (Built in Logic Block Observer BILBO)

#### Chapitre 1: Introduction

Pour les circuits de signaux analogiques et mixtes, le développement d'un outil efficace de diagnostic automatisé est indispensable et par la force des choses est toujours considéré comme un domaine de recherche ouvert. Le diagnostic de défaillance des circuits analogiques est beaucoup plus compliqué que celui des circuits numériques. Les principales raisons sont les mauvais modèles de défaut, la non-linéarité, la mesure des tensions et des courants aux nœuds internes qui sont parfois inaccessibles et l'ambiguïté qui s'installe dans les mesures et l'analyse des réponses du sujet défaillant. L'ambiguïté résulte principalement en raison des tolérances dans les composants.

Pour toutes ces raisons, le diagnostic de défauts des circuits analogiques est relativement moins développé à cause de leur complexité et de l'inaccessibilité à leur structure interne. Par ailleurs, il est devenu très exhaustif par la diversité des paramètres à tester ce qui a rendu ce processus très consommateur de temps et d'argent. Le test analogique doit maintenant être accéléré en incluant l'autotest intégré (Built In Self Test: BIST) et accompagné par les approches de la conception pour la testabilité (Design For Testability: DFT) tout en faire les considérant comme partie du cycle de conception du processus de fabrication des circuits intégrés [2].

Les circuits analogiques font partie des applications dans de nombreux domaines comme les dispositifs de télécommunication sans fil, biomédical, l'électronique grand public, le réseautage, etc [3]. De nouvelles stratégies doivent être développées pour répondre aux besoins du test de ce type des circuits et cela exige une recherche substantielle pour développer des méthodes de diagnostic de défaillance analogique compatibles avec les méthodes numériques déjà développées pour atteindre la quantité désirée de diagnostic de défauts. Ces derniers sont importants en nombre et différents en nature, ce qui incite à donner une étude informative, les banalisant et les classifiant selon leur degré de sévérité.

#### 1.2. Classification des défauts

Les différents types de défauts des circuits analogiques peuvent être classés comme suit:

- a) des fautes catastrophiques ou des fautes dures.

- b) des fautes paramétriques ou soft.

Dans le cas des défauts durs, l'élément défectueux est soit court circuit, soit ouvert. Alors que pour les défauts paramétriques, la valeur de l'élément change ou s'écarte de sa valeur nominale sans atteindre les limites extrêmes. Les défauts paramétriques résultent principalement du vieillissement, des tolérances de fabrication ou des effets parasitaires.

#### 1.3. Classification des techniques de localisation des pannes

La catégorisation la plus populaire est basée sur l'étape à laquelle la simulation de processus de test est effectuée. Celui ci s'exécute soit par :

- a) Simulation avant test (Simulation Before Test SBT), ou

- b) Simulation après test (Simulation After Test SAT)

Figure 1.1 Techniques de classification de fautes [1]

#### 1.3.1. Simulation avant test (SBT)

Cette méthode met l'accent sur la construction du dictionnaire ou du répertoire de défauts dans lequel le comportement nominal du circuit opérant en régime statique (DC domaine), en domaine temporel ou en domaine fréquentiel est collectionné. Les réponses du circuit pour différents défauts prévus y sont également stockées. Les deux méthodes importantes dans l'approche SBT sont:

- technique du dictionnaire des fautes

- techniques statistiques

#### 1.3.1.1 Technique de dictionnaire de fautes

Cette technique consiste aux cas du circuit sous test en absence et en présence de défauts. L'anticipation des fautes est basée sur le domaine d'expérience acquise et l'efficacité de cette technique dépend de la façon dont les défauts sont anticipés. La simulation de fautes joue un rôle très important dans la construction de dictionnaires de fautes. Les facteurs qui décident de l'efficacité de cette technique sont le choix approprié de stimulus, la sélection de l'optimisation des mesures de test et l'isolement de défaut. La sélection d'un ensemble ou une série de mesure et de test qui peuvent être soit des points d'accès de test ( nœuds internes ou externes du circuits) ou des fréquences de test, est primordiale dans cette technique.

Le nombre de mesures de test est choisi pour isoler le nombre maximal de défauts. Ce critère peut parfois augmenter la taille du dictionnaire, car le but cherché est de détecter la majorité des défauts, entraînant malheureusement un plus grand nombre de mesures prises. L'optimisation est dans ce cas faite pour supprimer les mesures qui sont redondantes ou qui n'aident pas à l'isolement de défaut. Le dictionnaire des défauts est construit pour les états nominaux et défectueux du circuit testé. Les mesures sont effectuées à différents nœuds de test, ou à un seul nœud de sortie pour différentes fréquences de test. L'optimisation consiste à réduire le nombre de mesures de test effectuées, sans compromettre la capacité de diagnostic des pannes du système. Ceci aide à réduire la taille du dictionnaire de fautes, économisant ainsi des ressources de mémoire importantes et augmentant la vitesse à laquelle l'isolement de faute peut avoir lieu. Enfin, l'isolement de défaut a lieu en comparant (ou en recherchant) les lectures des résultats de mesure réelles du circuit avec le contenu du dictionnaire.

#### 1.3.1.2 l'approche statistique

Dans cette méthode, un grand nombre de simulations sont réalisées pour caractériser le réseau statistiquement et ainsi constituer une base de données ou un dictionnaire statistique exhaustif. Cela aide à arriver à la probabilité de fautes dans chaque composant du circuit.

Pendant la phase de test, le composant présentant la probabilité d'erreur la plus élevée est le composant défectueux le plus probable.

#### 1.3.2 Simulation après test (SAT)

Dans cette approche, la simulation est effectuée au moment du test. Ceci est fait pour identifier les paramètres du réseau. Les mesures de tension et de courant du circuit sont prises et elles sont ensuite utilisées pour arriver aux valeurs du composant. Les éléments défectueux sont ensuite identifiés en déterminant les composants qui tombent à l'extérieur de la plage de

#### Chapitre 1: Introduction

tolérance de conception. Ces méthodes sont appelées méthodes topologiques car elles supposent la connaissance de la topologie du circuit.

Comme on le voit dans la figure 1.1, les 3 méthodes principales de SAT sont:

- 1. technique d'identification des paramètres

- 2. technique de vérification des défauts

- 3. technique d'optimisation

#### 1.3.2.1 Techniques d'identification des paramètres

Ces techniques fonctionnent sur la base que les variables indépendantes disponibles sont suffisantes pour identifier tous les paramètres du réseau. Et sont classées comme linéaires et non linéaires selon la nature des équations de diagnostic. Parmi les techniques linéaires, celles qui sont généralement utilisées sont la technique de transformation Star-Delta et la technique de simulation des composants. Pour les techniques non linéaires, les méthodes utilisées sont les tests DC, le test en domaine temporel, le test multifréquences, etc. En général, la technologie non linéaire fournit une solution unique alors que les équations linéaires de diagnostic donnent une solution globale unique.

#### 1.3.2.2 Techniques de vérification des fautes

Si le nombre de mesures est limité, tous les paramètres ne peuvent pas être identifiés. Cette technique suppose que seuls quelques paramètres sont défectueux et que le reste des éléments du réseau sont dans leurs tolérances de conception et ne sont donc pas défectueux. Dans cette technique, la théorie des réseaux, la théorie mathématique et la théorie des graphes sont utilisées. Le processus utilisé dans cette technique considère que le circuit entier est divisé en deux groupes, nominativement le groupe 1 et le groupe 2. Ce regroupement se fait à chaque étape du test. Ici, l'un des groupes est supposé être constitué seulement de composants libres de défaut, tout comme l'autre groupe est composé de composants défectueux. Les mesures et les caractéristiques des composantes nominales du groupe 1 sont utilisées pour calculer les entrées et les sorties du groupe 2. Tous les composants du groupe 2 dont les paramètres d'entrée et de sortie sont compatibles avec ceux du groupe 1 sont déplacés vers le premier. Cette procédure est répétée jusqu'à ce qu'une vérification satisfaisante soit réalisée. D'autres techniques couramment utilisées sont énumérées comme technique de classement [4 - 6], nouvelle approche de décomposition [7 - 9], et technique liée à la faute [10 - 12].

#### 1.3.2.3 Méthode d'optimisation

Ces techniques sont utilisées pour trouver les éléments défectueux les plus probables [13, 14]. Parmi les méthodes populaires utilisées, la technique d'approximation quadratique qui permet d'identifier les éléments qui présentent de grandes déviations au delà de leurs valeurs nominales : ces éléments sont considérés comme défectueux.

L'approche SAT est moins populaire car elle nécessite une analyse numérique complexe, pour simuler des défauts et en particulier les défauts durs. De plus, il est possible que l'analyse numérique soit très sensible aux fautes, même minimes, dans la modélisation. L'approche SAT a souvent besoin d'énormes quantités de calculs et de relations algébriques compliquées. L'approche SAT présente parfois un échec lorsque les variations des composants sont comptabilisées.

En général, dans les circuits analogiques, seuls les défauts simples sont considérés, car ils nécessitent une simulation minimale. La procédure de test requise pour ce cas de défauts est aussi simple. Un circuit est considéré défaillant même si un seul et unique composant est défectueux, alors une simulation de fautes multiples n'est pas dans l'urgence à être utilisée pour décider si un circuit est défectueux ou non. Dans certains cas, l'apparition simultanée de deux défauts ou plus peut avoir un effet complémentaire et leur considération n'est pas à négliger.

#### 1.4 Diagnostic de défauts en analogique et en numérique

Les différences entre le diagnostic de fautes analogiques et numériques sont données cidessous [15]:

- Dans les circuits analogiques, la taille n'est pas un problème car le nombre de composants est relativement faible contrairement aux circuits numériques où le nombre de transistors est de dizaines de millions. Les entrées et sorties analogiques sont également petites.

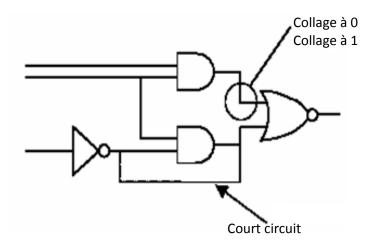

- La modélisation est plus difficile dans les circuits analogiques que dans les circuits numériques. Il n'y a pas de modèle de défaut largement accepté dans les circuits analogiques comme les modèles de collage à un et collage à zéro dans les circuits numériques.

- Dans les systèmes analogiques, la gamme de signaux est infinie.

- Les plages de tolérance dépendent des variations de processus, du vieillissement et des inexactitudes de mesure.

- Le bruit doit être pris en compte dans le diagnostic des fautes analogiques.

- En présence des fautes multiples, les effets s'annulent parfois. Ainsi, tous ces défauts peuvent ne pas être réels.

• La décomposition des composants n'est pas possible dans les circuits analogiques.

À l'avenir, les tests analogiques doivent prendre en charge les coûts minimaux, minimiser la surface des puces et avoir une vitesse de fonctionnement plus rapide [16].

#### 1.5 Problématique et objectif

L'objectif de ce travail est de proposer des méthodes d'optimisation du test des circuits analogiques. Ces méthodes doivent satisfaire les deux exigences primordiales :

- 1. la généralité : être applicable à tous les types de circuits quel que soit le nombre et la nature des tests ;

- 2. adaptabilité : travailler avec les données disponibles et pouvoir exploiter des données obtenues au cours du test.

#### 1.6 Organisation de la thèse

Motivé par les problèmes de recherche précédemment discutés, cette thèse vise à analyser et à élucider les restrictions des méthodes existantes et de recommander de nouvelles méthodes de détection et de classification des fautes des circuits analogiques. Plus précisément, la thèse est organisée comme suit.

Dans le chapitre 2, l'état de l'art sur les différentes techniques de test relatives aux circuits analogiques et numériques est présenté. Parmi ces techniques, on cite comme exemple les approches fonctionnelles et structurelles sur lesquelles nous nous sommes inspirés pour introduire notre approche afin de ramener certaines réponses aux questions chaudes que font apparaître les difficultés dans le test des circuits analogiques.

Le chapitre 3, fait l'objet d'une présentation descriptive des différents types de défaillances qui peuvent affecter les circuits intégrés et en particulier celui des circuits analogiques. Cette étude servira sans doute à l'établissement d'un diagnostic des défauts basé sur le concept de la modélisation depuis le bas niveau d'abstraction des circuits analogiques jusqu'au niveau fonctionnel ou comportemental, tout en mettant l'accent sur le fond des problèmes que rencontrent les spécialistes dans le domaine du test des circuits analogiques.

Au chapitre 4, différentes techniques sont proposées pour détecter les défauts de composants dans les circuits intégrés analogiques et de maximaliser le taux de couverture des fautes. Ces techniques sont validées par applications sur différents circuits sous test pour les deux types de fautes (catastrophiques et paramétriques).

Le chapitre 5 concerne la classification des fautes des circuits analogiques en utilisant des algorithmes d'intelligence artificielle. Les limites des méthodes existantes de détection et de

#### Chapitre 1: Introduction

classification des fautes sont expliquées. Les blocs de construction du classificateur neuro-flou multi-classes sont présentés (classificateur flou et classificateur de réseau neural). Ce dernier est proposé pour la détection et la classification des défauts dans les circuits analogiques. Le classificateur proposé est comparé à celui du réseau neuronal artificiel (ANN) et à ceux d'autres méthodes. La validation de ce classificateur a été faite sur trois circuits de tailles et structures différentes.

En fin le chapitre 6 clôture cette thèse par une conclusion qui parachèvera le travail entrepris. A travers celle ci on a précisé les points positifs qui en découlent suivis de conseils et de recommandations qu'il faut prendre en considération dans des futurs travaux de recherche.

#### 1.7 Contributions

Cette thèse montre quelques contributions de recherches clés et des améliorations scientifiques sur les solutions existantes et qu'on énumère comme suit :

- 1. Tout d'abord, de nouvelles entrées ont été introduites aux classificateurs.

- 2. Un nouveau traitement pour les entrées du classificateur est présenté, qui au préalable commence par la considération d'un nombre considérable d'entrées et ensuite finit par réduire celui ci en employant des caractéristiques techniques de réduction des dimensions. Cette solution alternative permet d'économiser beaucoup de temps pour le développement des classificateurs.

- 3. Dans la méthode proposée, certains modèles de fautes sont utilisés, et par conséquent arrivent à détecter toutes les fautes possibles.

- 4. Enfin, un classificateur neuro-flou multi-classes est développé pour une discrimination entre plusieurs types de défauts et validé selon trois exemples de circuits sous test.

# Chapitre 2

# Etat de l'art du test des circuits intégrés

## **CHAPITRE 2**

# Etat de l'Art du test des circuits intégrés

#### 2.1 Introduction

Les équipements électroniques englobant les circuits électroniques sont classés en circuits analogiques et numériques [17], [18]. Selon une statistique, près de 80% des circuits électroniques dans les équipements électroniques sont numériques, mais environ 80% des défauts se produisent principalement dans les parties analogiques. Les circuits numériques se composent généralement de composants d'une bibliothèque limitée à des modèles très simples. En comparant les circuits numériques et les circuits analogiques, le diagnostic des défauts des circuits numériques est plus facile que celui des circuits analogiques puisque les procédures de test pour le premier type de circuits sont bien définies et que le nombre limité de défauts tels que les défauts de type court-circuit, circuits ouverts et de collage sont connus et facile à traiter. Tandis que, dans les circuits analogiques, le diagnostic de défaut est très difficile en raison des caractéristiques de base des circuits analogiques tels que la non-linéarité et la tolérance des composants, les modèles de défauts inefficaces, les nœuds accessibles inadéquats et l'incertitude dans les mesureurs. Pour ces raisons, plus d'attention et d'efforts sont nécessaires pour le diagnostic de défaut des circuits analogiques.

Communément, les obstacles dans les circuits analogiques qui posent de grandes difficultés dans les stratégies de test se résument ainsi :

1) les informations dans le circuit analogique sont effectuées dans la forme du signal. La faible perturbation du signal peut affecter de façon significative la performance des circuits analogiques.

2) Du point de vue physique, les composants dans le circuit analogique sont communément non linéaires dans un large éventail de conditions de fonctionnement.

La validation des fautes dans les circuits analogiques linéaires et non linéaires est également problématique. Cela rend le diagnostic de défaut dans les circuits analogiques un problème ouvert et un grand domaine de recherche est émergé. L'approche de test dans le circuit analogique est généralement classée en deux types: test piloté par la spécification et test commandé par le défaut. Dans le premier type de test , la fonctionnalité du système est vérifiée et le circuit à tester doit satisfaire à l'exigence du système. Dans le test commandé par le défaut, l'intention première est de localiser les composants défectueux qui deviennent la principale raison de la défaillance du système. La détection automatique des pannes dépend des observations des réponses des circuits et des caractéristiques. Les méthodes pour le diagnostic de défaut sont généralement classées en deux catégories: simulation après test (SAT), simulation avant test (SBT) [19,20].

L'approche SBT est une sorte de processus de recherche, dans lequel la réponse de test attendue du circuit sous test est simulée. À la réception des données de test réelles par l'ingénieur de test, une comparaison des résultats de simulation du circuit sous les conditions de présence et d'absence de fautes est accomplie pour localiser les fautes dans les circuits. Les méthodes de l'approche SBT sont classées en deux types: les techniques de dictionnaire des fautes et les techniques statistiques [21].

La technique de dictionnaire de fautes: le dictionnaire de fautes est une liste de données émanant de la recherche qui consiste à l'investigation des cas défectueux et non défectueux du circuit sous test. La simulation de fautes a un rôle important dans la construction des dictionnaires. D'autres facteurs qui décident l'efficacité de cette approche sont : la sélection appropriée du stimulus, l'isolation de défaut et le choix de la mesure de test.

Dans l'approche SAT, la simulation du circuit est faite après avoir obtenu les données de test. Elle vise à modéliser le problème de diagnostic de défaut par une équation non-linéaire. Les variables et les paramètres des composants que régit cette équation sont déterminés à partir des données de test calculées. Ici, la simulation se déroule pendant les tests. L'identification de l'élément défectueux est obtenue en déterminant les composants dans les circuits dont les valeurs tombent en dehors de la tolérance de conception. La méthode SAT est également considérée comme une méthode topologique car elle présume les informations sur la topologie du circuit. Ici, les méthodes de simulation sont classées en trois types: méthode d'identification des paramètres, méthode de vérification des pannes et méthode d'approximation.

#### Chapitre 2 : Etat de l'art du test des circuits intégrés

Dans la technique d'identification des paramètres, la simulation de fautes est effectuée en fonction de l'hypothèse que les variables indépendantes existantes sont suffisantes pour trouver les paramètres du circuit entier. En se basant sur la nature de l'équation de diagnostic, cette technique est classifiée comme étant linéaire et non linéaire.

La technique de vérification des défauts, quant à elle, intervient lorsque le nombre de mesures dans le circuit est limité et que l'identification de tous les paramètres devient difficile. Avec cette technique il est supposé que peu de paramètres soient défectueux. Le reste des éléments dans les circuits sont considérés comme étant dans leur gamme de tolérance lors de conception, et ils sont donc considérés comme des éléments sans fautes.

La technique d'approximation est une technique qui vise à localiser les éléments défectueux d'une façon presque certaine. On dénombre peu de techniques de ce genre qui sont : la probabilité inverse, la technique d'approximation quadratique et les techniques d'approximation non réciproque.

L'approche SBT est populaire par rapport à l'approche SAT pour les raisons suivantes; dans celle ci, la simulation des fautes dures nécessite une analyse numérique complexe. L'erreur légère qu'elle soit dans la modélisation basée sur SAT induit une énorme variation dans l'analyse numérique. Le calcul et l'exigence d'une relation algébrique compliquée que requiert l'approche SAT constitue un fardeau dans ce type diagnostique. Lorsque les variations dans les composants sont comptabilisées pour la modélisation des défauts, l'approche SAT échoue.

La méthode de diagnostic SBT reste simple et facile à entreprendre par rapport à l'approche SAT, et elle présente un tas d'avantages dont on cite quelques uns :

- 1) Elle peut obtenir les paramètres de circuit dans plusieurs conditions de défauts, tandis que, dans l'approche SAT, la plupart des techniques assument seulement le paramètre défectueux sans considérer les paramètres entiers présents dans les circuits.

- 2) Dans l'approche SBT, les paramètres dans les circuits typiques dépendent de plus en plus de l'état de la faute.

- 3) La technique SBT est extrêmement efficace pour le test et diagnostic en ligne.

- 4) Les défauts anticipés et le circuit nominal sont simulés séparément, comblant ainsi la possibilité de détection des fautes.

- 5) Elle contribue à réduire le coût principal du processus de détection des fautes.

- 6) L'approche SBT a besoin plus de calcul avant la fonction de test.

#### 2.2 Généralités

#### 2.2.1 Définitions de la faute

Les définitions classiques de la faute sont:

- 1) Une faute est définie comme une déviation non autorisée d'au moins une propriété caractéristique ou un paramètre du système à partir de la condition acceptable/habituelle/standard [22].

- 2) La faute est toute agrégation d'éléments connexes qui forment ensemble une entité de complexité suffisante pour laquelle il est impossible de traiter tous les éléments au plus bas niveau de détail [18].

- 3) Une faute est un changement inattendu ou un dysfonctionnement dans un système, bien qu'il ne puisse pas entraîner une défaillance physique ou une panne [23].

- 4) Le terme «faute» ne peut se référer qu'à une déviation par rapport au modèle attendu du phénomène [24].

- 5) La faute est généralement définie comme le changement de la valeur nominale affectant sensiblement la performance du circuit menant à la défaillance du circuit [25].

Comme il n'existe pas de terminologie standard pour les termes utilisés dans le domaine du test analogique, et afin de faciliter la lecture de ce manuscrit, on donne ici quelques définitions de termes importants utilisés :

- **Défaut**: défaut physique qui affecte le layout d'un circuit.

- **Défaut de Spot (Spot defect)**: représente le dépôt supplémentaire ou insuffisant d'un ou plusieurs matériaux sur le "wafer", ceci engendrera le défaut physique.

- Faute: modélisation d'un défaut physique dans le but de simuler l'effet de ce dernier sur le circuit.

- Faute catastrophique: modélisation électrique d'un défaut majeur comme un courtcircuit ou un circuit ouvert entrainant le circuit vers le hors usage.

- Faute paramétrique: modélisation électrique des fluctuations de l'environnement de fabrication et des imperfections des paramètres du circuit qui engendrent des variations sur les sorties de celui ci.

- **Test fonctionnel**: Vérification des spécifications du circuit. Le but du test fonctionnel est de vérifier le fonctionnement du circuit avant de l'envoyer en production. En général, on effectue le test fonctionnel sur les prototypes des circuits.

- **Test structurel**: Vérification des circuits dans la phase de production en grande série, ceci est aussi appelé test de production. Le but du test structurel est de détecter les défauts de fabrication qui peuvent affecter le routage de circuit (lay-out).

- **Diagnostic**: Détermination de la cause du dysfonctionnement d'un circuit.

- **Génération déterministe**: Utilisation d'algorithmes pour trouver des tests qui détectent des fautes données, de façon déterministe.

- Optimisation d'un ensemble de tests: Réduction du nombre de vecteurs de test d'un ensemble, tout en détectant les mêmes fautes que l'ensemble de départ. Le but de l'optimisation des tests est de réduire le temps nécessaire à l'application de l'ensemble des tests par des équipements de test très coûteux, et réduire ainsi le coût du test de production.

- **Taux de couverture**: Le rapport du nombre de fautes détectées par rapport au nombre de fautes globales. Le taux de couverture dépend du modèle de faute utilisé.

#### 2.2.2 Types de fautes

Les fautes dans les circuits analogiques sont classées en fautes dures et fautes non sévères (soft faults). Les fautes dures, également connues sous le nom de fautes catastrophiques, provoquent un échec catastrophique du circuit. Le composant défectueux subissant ce genre de fautes peut être considéré comme par exemple court-circuité ou en circuit ouvert. Ce type de fautes peut également se produire en raison d'une grande variation dans le paramètre de conception des éléments de circuit. Les exemples des fautes dures dues à la variation des paramètres incluent la valeur du gain en courant (β) des transistors BJT et la longueur(L) et la largeur (w) du canal du transistor MOSFET. La cause majeure de la défaillance catastrophique est la déformation structurelle ou des paramètres extrêmes de la plage qui conduisent à la défaillance complète des circuits. La faute dure dans le circuit pourra être provoquée par des phénomènes de contamination de particules ou d'électro-migration se produisant dans les couches de conduction et de métallisation.

Les fautes non sévères (soft faults) sont également appelées les fautes paramétriques. La valeur de l'élément change ou dévie de sa valeur nominale sans dépasser les limites provoquant en conséquence une faute paramétrique. La performance du circuit est dégradée en raison de ce type de fautes. La déviation de la valeur nominale en dehors de la bande de tolérance prescrite est due au vieillissement du circuit, aux tolérances ou aux effets parasitaires dans les circuits.

#### 2.2.3 Sources de fautes

Les sources des fautes dans les circuits électroniques sont les courts circuits, les circuits ouverts et les erreurs des composants, qui sont les plus fréquents dans les circuits intégrés (C.I.). Même si la taille du circuit est petite telle que celle des C.I. de type S.S.I (Small Scale Integration), le nombre de composants présents dans les circuits est important. Les modifications fortuites relatives à la connexion terminale des composants du circuit génèrent la faute de court circuit ou de circuit ouvert.

Le court-circuit est un type de défaut dur. Le défaut de court-circuit est dû à la liaison non désirée entre les bornes des composants dans le circuit. Il court-circuite efficacement les éléments particuliers du circuit. Par exemple, une résistance de  $1\Omega$  (ohm) liant deux points de connexion d'un composant du circuit est capable de simuler un défaut de court-circuit. La défaillance due à ce défaut entre les circuits du réseau de l'équipement électronique est l'une des principales sources de défaillance des circuits électroniques.

La faute du circuit ouvert est également une sorte de défauts durs qui entraine un changement catastrophique du circuit. Ce genre de défauts se produit dans le circuit lorsque la borne de composant n'est nullement en contact avec d'autres parties du circuit. A titre d'exemple une borne de contact à la sortie de circuit résultera en une génération d'une résistance très élevée à l'apparition du défaut dans le circuit. Ce type de défaut causé au niveau de la borne de contact de la sortie du composant est également une des principales sources de défaillance dans les circuits électroniques. Physiquement ce genre de fautes ne peut être que le résultat d'une patte de composant en l'air ou une coupure de ligne de connexion ou une fissuration d'une jonction d'un transistor. En phase de conception fondée sur le processus de simulation, il est presque impossible de produire une coupure ou défaire une liaison entre deux points de contact au niveau du circuit; le simulateur impliqué dans ce processus le réfutera. La solution alternative que cet outil de conception peut admettre est de modéliser ce défaut électrique par une résistance de  $1 \text{ } M\Omega$  (Méga-ohm) ou plus au niveau de la rupture de la liaison des composants dans le circuit.

Fautes des composants: les composants présents dans les circuits électroniques peuvent également être une raison de défauts dans ces circuits. Si une résistance est défectueuse dans le circuit, le circuit global devient défectueux à cause de cette résistance. Un tel composant produit une erreur dans le fonctionnement des circuits. Dans les circuits électroniques, l'erreur de composant est également une source majeure de la faute : elle est appelée erreur du composant.

#### 2.2.4 Simulation de fautes

Le but d'un simulateur de fautes est de déterminer les effets des défauts sur le comportement du circuit et d'évaluer la qualité des jeux de vecteurs de test en calculant le taux de couverture obtenu selon un modèle de faute donné. Les simulateurs de fautes pour les circuits numériques utilisent des techniques connues comme la simulation de fautes parallèles ou la simulation de fautes concurrentes qui exploitent le fait qu'on utilise des simulations logiques et que les différences entre le bon circuit et le circuit fautif sont minimes. Ces techniques permettent de réduire considérablement le temps nécessaire à la simulation de toutes les fautes. Malheureusement, ces techniques sont ou bien mal adaptées ou difficilement utilisables pour les circuits analogiques.

L'approche la plus utilisée pour la simulation de fautes des circuits analogiques est basée sur l'utilisation d'un simulateur pour les circuits analogiques comme SPICE, ELDO et CADENCE... etc. La méthode consiste à exécuter les étapes suivantes :

- Simulation du bon circuit

- Injection de faute dans le circuit

- Simulation du circuit fautif

- Comparaison des résultats des deux simulations

Les premiers simulateurs de fautes adoptant cette approche sont FSPICE [95] qui repose sur le simulateur du domaine public SPICE, et ANAFAULT [43] qui utilise le simulateur commercial ELDO de Mentor Graphics. Comme les simulateurs électriques de type SPICE sont très lents dans leur processus de calcul pour des circuits analogiques de plus en plus complexes dans leur structure, des simulateurs de fautes spécifiques ont été développés dans le but d'accélérer la simulation de fautes pour certaines classes de circuits.

#### 2.3 Tâches des systèmes de diagnostic des fautes

Un système de diagnostic des fautes surveille et détecte les défauts et identifie leur emplacement dans les circuits analogiques ou autres qu'ils soient correctement conçu [23]. Un diagnostic peut prévenir les conséquences graves en raison de la propagation de l'effet de faute dans le circuit provenant de leur lieu de localité des étages antérieurs. Les principales fonctions des systèmes de diagnostic des fautes sont :

✓ détection des fautes: la tâche de détection des fautes est de découvrir le comportement anormal du circuit à cause de l'occurrence des défauts. Ceci est entrepris en comparant les réponses des circuits fautifs et les circuits libres de fautes.

#### Chapitre 2 : Etat de l'art du test des circuits intégrés

- ✓ isolement des défauts l'isolement des fautes: l'isolation des fautes mappe la région physique du circuit où le défaut est détecté pour identifier le positionnement des composants défectueux dans le circuit.

- ✓ identification des défauts : les composants défectueux du circuit testé sont identifiés

à l'aide de la tâche d'identification des défauts.

- ✓ prédiction de défauts: la tâche de prédiction surveille continuellement la réponse du circuit et prédit la variation de la performance du circuit. La variation de paramètre du circuit testé est également surveillée de façon non linéaire.

- ✓ explication de défauts: la tâche d'explication est la tâche de génération d'information concernant le défaut dans le circuit. Il facilite le test pour comprendre la relation entre le diagnostic actuel et les indications du circuit.

- ✓ **simulation de défauts:** dans la simulation de défaut, le défaut hypothétique dans le circuit est simulé en utilisant la sortie du modèle de faute de l'étape d'identification des fautes.

#### 2.4 Les différents types de tests

- Test fonctionnel : vérification des spécifications du circuit.

- Test structurel : il permet de détecter les défauts de fabrication qui peuvent affecter le fonctionnement des circuits.

- Test paramétrique : il est utilisé pour vérifier si certains paramètres du circuit sous test sont dans la plage des valeurs requises.

- Test alternatif : test qui permet de calculer (ou prédire) les performances du circuit à partir de tests plus simples.

- Test statique : vérification des états stationnaires du système sous test.

- Test dynamique : vérification des caractéristiques dynamiques du système sous test.

- Test exhaustif : vérification de tous les modes d'opération pour tous les types de fautes.

- Test en ligne (test on-line) : le test est effectué pendant le fonctionnement normal du circuit.

- Test hors ligne (test off-line) : le test est effectué en mode test.

- Test concurrent : le test est effectué pendant l'opération.

- Test semi-concurrent : le test est effectué pendant l'opération mais aussi pendant le temps de repos.

- Test non-concurrent : le test est effectué hors-ligne.

#### Chapitre 2 : Etat de l'art du test des circuits intégrés

- Test wafer : le test est effectué au niveau plaquettes (Wafer) pendant la fabrication des circuits intégrés.

- Test de production : test qui se fait durant la phase de production des circuits intégrés.

- Test sur puce (on-chip) : un test qui s'effectue dans la puce et à l'aide d'un ensemble de circuits qui se trouvent à l'intérieur de la même puce.

- Test in-field: un test qui s'effectue une fois la puce est dans son application finale.

#### 2.4.1 Difficultés de test des circuits analogiques

Les propriétés naturelles des signaux analogiques et la complexité de test analogique sont considérés comme des facteurs les plus dominants en matière de difficultés rencontrées dans ce domaine. Beaucoup de choses ont été dites sur ce sujet et la bibliographie qui y est relative s'est richement étalée la dessus que nous nous sommes contraint d'en discuter ici que sur certaines difficultés majeures et qui se résument comme suit [26 - 29]:

- 1) les signaux analogiques sont le temps et l'amplitude continus dans la nature. Contrairement aux signaux numériques, qui ne sont représentés que par deux valeurs (basse et haute), les signaux analogiques sont représentés en principe par un nombre infini de valeurs qui présentent des informations de signal. Les signaux analogiques sont des formes d'onde très sensibles, même une petite perturbation au niveau des magnitudes de signal peut causer une grave dégradation de la qualité du signal.

- 2) Les circuits analogiques sont des dispositifs électriques intrinsèquement non linéaires. L'utilisateur suppose que le circuit non linéaire peut disposer de région de son espace d'entrée qu'il lui permet de fonctionner linéairement. En outre, les caractéristiques entrées/sorties non linéaires des circuits analogiques nécessitent des techniques sophistiquées pour résoudre les équations non linéaires qui décrivent le comportement du circuit telles que par exemple, des méthodes itératives de résolution d'équations non linéaires d'une analyse transitoire dans les circuits analogiques.

- 3) La relation entre l'entrée et la sortie dans les circuits analogiques est très compliquée par rapport à celle des circuits numériques qui peut être décrite par la table de vérité ou des équations booléennes, et qui par conséquent est simplifiée et facile à modéliser.

- 4) Les circuits analogiques peuvent être décrits dans plusieurs domaines tels que les domaines de fréquence et de temps. Chacun de ces domaines présente ses propres spécifications et méthodologies pour décrire les circuits analogiques.

- 5) Dans les circuits numériques, seules quelques spécifications doivent être mesurées (temps de montée, temps de descente, temps de retard, tension de seuil logique, etc.).

Ces spécifications sont généralement les mêmes pour tous les circuits numériques et indépendantes des applications. En revanche, les circuits analogiques et mixtes comprennent plusieurs types de classes ou de modèles, par exemple les filtres, les amplificateurs opérationnels, les convertisseurs A/D et D/A, les boucles à verrouillage de phase, etc. Chaque classe de circuit a en prévision un ensemble séparé de caractéristiques différentes qui la distingue des autres classes. En outre, ces spécifications dépendent aussi d'une application particulière, où un même circuit y est impliqué. Ainsi, la vérification des paramètres liés à ces spécifications peut généralement être coûteuse et longue.

- 6) Les valeurs des éléments de circuit varient considérablement, ce qui est dû aux variations du procédé de fabrication. Par conséquent, la fonctionnalité du circuit dépend de ces variations, et le circuit analogique est conçu pour dépendre de la gamme des valeurs d'élément en rapport avec ces paires dans le circuit plutôt que des ces valeurs en tant que composant individuel. La gamme acceptable de valeurs d'élément et de fonctionnalité de circuit, appelée tolérance, dépend de plusieurs facteurs telles que les applications prévues, les inexactitudes de simulation et les erreurs de la mesure.

- 7) La complexité du modèle de fautes dans les circuits analogiques et mixtes est différente de celle des circuits numériques. Dans les circuits numériques, le modèle de « collage à la faute » est largement utilisé au niveau de la porte logique [30]. En revanche, dans les circuits analogiques, des modèles de défauts analogiques précis ne sont pas toujours disponibles et s'ils le sont restent confinés à l'échelle micrométrique (niveau de jonctions) ou à la limite à celui de composants primitif (transistor, diode etc). Par ailleurs, la description du circuit sain ou défectueux pour tout type de défauts à des niveaux plus élevés comportementaux ou fonctionnels qu'ils soient par un modèle à l'échelle macro (macro-modèle) est devenue une nécessité. Seulement cette tache est très compliquée à mettre en œuvre et reste encore un défi dans le test de circuits analogiques. Plusieurs modèles de fautes à différents niveaux d'abstraction sont proposés. En outre, les méthodes de probabilité ne sont souvent pas efficaces parce que les distributions statistiques des défauts analogiques, généralement, ne sont pas connues avec suffisamment de précision pour prédire d'une façon précise la couverture de défaut d'un ensemble de test.

- 8) Comme la technologie est restreinte dans son développement concernant la cohabitation entre deux environnements différents ou les circuits analogiques et numériques coexistent sur une seule puce (System-on-a-Chip), l'accessibilité aux nœuds

de circuit (broches des circuits intégrés) est réduite. Donc la contrôlabilité et l'observabilité des nœuds de circuit sont réduites. Cette croissance de l'intégration exige des techniques de modification de la conception telles que la conception pour la testabilité (Design For Test DFT) et l'autotest intégré (Built In Self Test : BIST) pour assurer une plus grande testabilité des circuits analogiques.

- 9) Les méthodologies DFT et de génération de test automatique (ATPG) standard aux signaux mixtes ne sont pas disponibles. Chaque entreprise de l'industrie des circuits intégrés (C.I.) possède ses propres méthodes d'accès aux nœuds de test et de génération de signaux de test. L'absence de normes conduit à un long cycle de conception, long temps de développement de test, et l'augmentation du temps au marché (time to market).

- 10) il n'y a pas d'accord général dans la communauté de conception analogique entre les niveaux d'abstraction réelle et la hiérarchie à utiliser dans l'automatisation de ce type de conception

- 11) en plus des problèmes mentionnés ci-dessus, il y a d'autres problèmes dans le test de circuits analogiques et mixtes tels que les erreurs de mesure, les effets sonores aléatoires, l'effet de la charge de la sonde de mesures, et les conditions ambiantes comme la température.

L'importance de chacune de ces difficultés n'est pas la même et varie d'un type de test à un autre. La diversité des spécifications de caractérisation d'un circuit analogique et l'absence de modèles de défaut sont considérées comme des questions les plus critiques. Toutes ces difficultés font de l'automatisation du processus de test analogique une tâche très compliquée. Ceci explique également pourquoi de nos jours le test analogique est loin derrière son homologue numérique. En outre, ces difficultés conduisent à la nécessité de produire des équipements d'essai analogiques très coûteux pour obtenir des mesures précises du signal.

#### 2.4.2 Génération de test

Le test est une procédure de détection et / ou de localisation des fautes. Les tests sont divisés en deux catégories : les tests de détection de fautes et les tests de diagnostics. La première catégorie nous renseigne sur la présence ou l'absence de fautes mais elle ne fournit aucune information sur l'identité de la faute et de sa localisation. Un test de diagnostic, quant à lui, détermine la position de la faute, les types de fautes et il peut même fournir d'autres informations, tels que la nature de défauts, les stimuli de leur détection etc.... Le processus de génération de test comporte le modèle de faute, la génération de vecteurs de test, la simulation de faute, l'évaluation de la couverture de faute, et l'élaboration du dictionnaire de faute.

La première étape de ce processus de génération de fautes consiste à développer un dictionnaire de faute pour le circuit à tester, c'est à dire modéliser les fautes et réduire leurs nombres en termes de relation d'équivalence entre elles. Souvent le modèle de collage à une faute singulière / prise individuellement est adopté puis le dictionnaire de faute est généré directement à partir de la description du circuit logique tout en arrangeant les fautes pour chaque porte, sous une forme tabulaire.

Les vecteurs de test sont alors générés pour vérifier l'ensemble de fautes listées dans ce dictionnaire. Ces vecteurs sont alors simulés pour les circuits en mauvais fonctionnement puis mentionnés et contenus dans cette liste de fautes et enfin la couverture de ces dernières est évaluée à partir des résultats de la simulation de fautes. Si cette couverture de fautes est inadéquate, alors le processus de génération de vecteurs de test et de simulation de fautes est répétée pour les fautes non testées jusqu'à l'obtention d'une meilleure détection. Finalement, le dictionnaire de fautes est complété par la spécification d'information suffisante pour la détection et la localisation de fautes. Pour des circuits de petite taille ou faible intégration (small scale integration S.S.I.), la procédure de test peut se faire manuellement sans aucune difficulté. Seulement, la croissance en complexité des circuits électroniques et leur intégration à des échelles très élevées sur une même puce de silicium (Les circuits LSI, VLSI) a rendu cette tâche très délicate et très exhaustive. En conséquence, beaucoup d'information nécessite d'être collecté dans cette phase de test et une forte consommation de temps en suit. Ceci conduira effectivement à une hausse vertigineuse du coût du test. L'introduction de l'outil informatique dans ce domaine de test est d'un apport fort appréciable quant à la rapidité, la préservation de l'information et la réduction du coût du processus du test. Ceci est devenu alors totalement automatisé.

Ces phases sont alors assurées par cet outil informatique et consistent à la génération des vecteurs de test, la description du bon circuit, la simulation et modélisation des défauts possibles pouvant affecter ce circuit, le diagnostic etc. . Toutes ses fonctions ainsi réunies constituant ce qu'on appelle "Le processus automatique de génération de modèle de test", ATPG (Automatic Test Pattern Generation).

#### 2.4.3 Classification des tests

La préparation des tests des systèmes électroniques nécessite la description des circuits à tester, et à minimiser la liste et les caractéristiques des outils élémentaires. A partir de là, on peut répartir les tests en deux grandes catégories :

- a- Le test analogique: test qui concerne tout les circuits construits de composants aussi bien passifs que actifs réunis de façon à accomplir des fonctions analogiques.

- b Le test numérique: test qui concerne les circuits digitaux et numériques (portes logique, circuits microprocesseurs, PIC, mémoires ....) et qui sont conçus à produire des fonctions logiques et séquentielles.

#### 2.4.4 Couverture d'un test

Cette phase de test est en général conçue des programmes de génération de tests fournissant une séquence de vecteurs capables de détecter un ensemble connu de défauts ; il peut arriver qu'un programme n'arrive pas à trouver de vecteurs capables de détecter des défauts présumés du circuit. L'exhaustivité des tests est alors dite inférieure a 100 %. Sa valeur est égale au rapport donné par l'équation (2-1) [31].

$$N = \frac{nombre \ de \ fautes \ detect\'ees}{nombre \ total \ de \ fautes}$$

(2-1)

Dans certains, cas il peut être nécessaire de mesurer l'exhaustivité des vecteurs de tests parce qu'ils ont été crées manuellement par les concepteurs pour une vérification fonctionnelle ou pour améliorer la qualité du test généré. Le calcul de l'exhaustivité est accompli par emploi d'un simulateur de fautes utilisant un algorithme concurrent qui détermine le nombre de fautes détectables par l'ensemble de vecteurs de tests disponibles.

#### 2.4.5 Qualité des tests

Le niveau de confiance d'un test dépend de la qualité du test qui a été appliqué, l'idéal est de 100%. Compte tenu de la complexité de certains tests, l'objectif fixé sur le plan de test est légèrement en deçà de ce pourcentage; c'est un compromis entre le coût de génération et d'application du test et le coût résultant de la limitation de l'exhaustivité du test.

#### 2.4.6 Testabilité

La notion de Testabilité est définie comme étant un moyen de mesure de l'efficacité de test de circuit défectueux, c'est-à-dire un moyen qui parvient à détecter et à localiser l'origine de la panne au sein du circuit. [31, 32]

Pour faciliter le test, il existe plusieurs paramètres à définir mais on ne cite que les plus importants à savoir la contrôlabilité et l'observabilité des nœuds.

- a) La contrôlabilité: C'est l'aptitude de contrôler la défaillance au niveau d'un nœud à partir de ses entrées primaires.

- b) L'observabilité: C'est l'aptitude de faire propager la valeur d'un nœud défectueux sur une sortie primaire.

Ces deux aptitudes sont alors mesurées en respectant les deux règles de testabilités suivantes:

#### > Règles globales de testabilité

- Utiliser la hiérarchie du circuit.

- Partitionner le circuit en unités testables homogènes par exemple PLA (Programmable Logic array), mémoire, logique combinatoire pure.

#### > Règles locales de testabilité

- Bloquer toutes sources d'horloge locale.

- Décomposer en sous-ensembles séquentiels qui ne nécessitent pas de longues séquences d'initialisation.

- Se ramener, dans la mesure du possible, à des ensembles combinatoires pour les circuits logiques.

#### 2-5 Modélisation des fautes analogiques

Pour générer des vecteurs de test dans un ensemble électronique, il est nécessaire de modéliser les défauts les plus probables, c'est a dire de leur faire correspondre des types de défauts théoriques produisant les même anomalies de fonctionnement du circuit que les défauts réels.

Les modèles sont des représentations des défauts physiques qui peuvent être détectés dans un composant quelconque. Ils peuvent prouver et déterminer la qualité des ensembles électroniques sous test et les faire comparaître aux modèles orignaux, nous permet d'évaluer quelques spécifications concernant leur comportement avant et durant le test, pendant leur bon ou mauvais fonctionnement. De cette façon le test devient plus simple et moins compliqué surtout du coté analogique des circuits.